# **GigaDevice Semiconductor Inc.**

# GD30LD1003x 2A High-accuracy, Low Noise LDO

Datasheet

## **Table of Contents**

| T | able  | e of Contents2                                                                                                                                                |  |  |  |  |  |  |  |

|---|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| L | ist c | of Figures4                                                                                                                                                   |  |  |  |  |  |  |  |

| L | ist c | of Tables5                                                                                                                                                    |  |  |  |  |  |  |  |

| 1 | F     | Features6                                                                                                                                                     |  |  |  |  |  |  |  |

| 2 | Α     | pplications6                                                                                                                                                  |  |  |  |  |  |  |  |

| 3 | G     | eneral description6                                                                                                                                           |  |  |  |  |  |  |  |

| 4 | D     | evice overview                                                                                                                                                |  |  |  |  |  |  |  |

|   | 4.1   | Device information8                                                                                                                                           |  |  |  |  |  |  |  |

|   | 4.2   | Block diagram8                                                                                                                                                |  |  |  |  |  |  |  |

|   | 4.3   | Pinout and pin assignment9                                                                                                                                    |  |  |  |  |  |  |  |

|   | 4.4   | Pin definitions9                                                                                                                                              |  |  |  |  |  |  |  |

| 5 | F     | unctional description11                                                                                                                                       |  |  |  |  |  |  |  |

|   | 5.1   | Output Voltage Setting11                                                                                                                                      |  |  |  |  |  |  |  |

|   | -     | Recommended device selection         11           2.1         CIN and COUT Selection         11           2.2         Feed-Forward Capacitor (CFF)         11 |  |  |  |  |  |  |  |

|   | 5.3   | Low-Noise, High-RSRR Output12                                                                                                                                 |  |  |  |  |  |  |  |

|   | 5.4   | Power-Good Function12                                                                                                                                         |  |  |  |  |  |  |  |

|   | 5.5   | Soft-Start Function13                                                                                                                                         |  |  |  |  |  |  |  |

|   | 5.6   | Undervoltage Lockout (UVLO)14                                                                                                                                 |  |  |  |  |  |  |  |

|   | 5.7   | Power Dissipation (P <sub>D</sub> )15                                                                                                                         |  |  |  |  |  |  |  |

| 6 | Ε     | lectrical characteristics16                                                                                                                                   |  |  |  |  |  |  |  |

|   | 6.1   | Absolute maximum ratings16                                                                                                                                    |  |  |  |  |  |  |  |

|   | 6.2   | Recommended Operating Conditions16                                                                                                                            |  |  |  |  |  |  |  |

|   | 6.3   | Electrical sensitivity17                                                                                                                                      |  |  |  |  |  |  |  |

|   | 6.4   | Electrical Specifications17                                                                                                                                   |  |  |  |  |  |  |  |

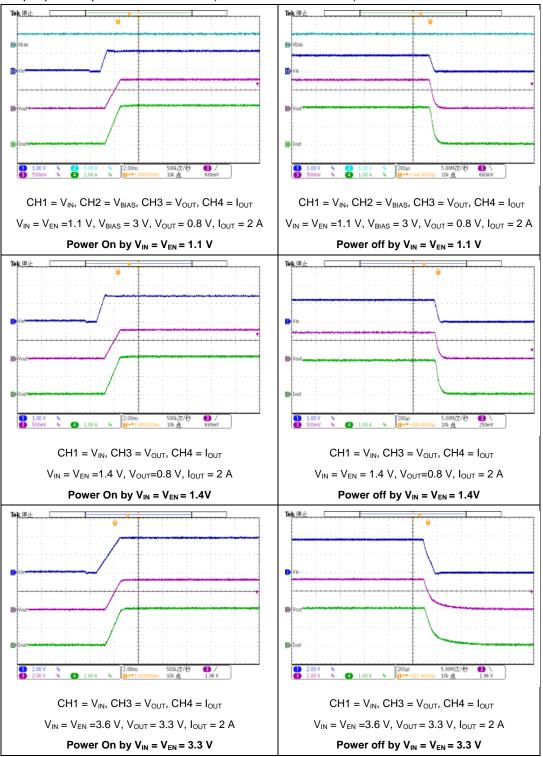

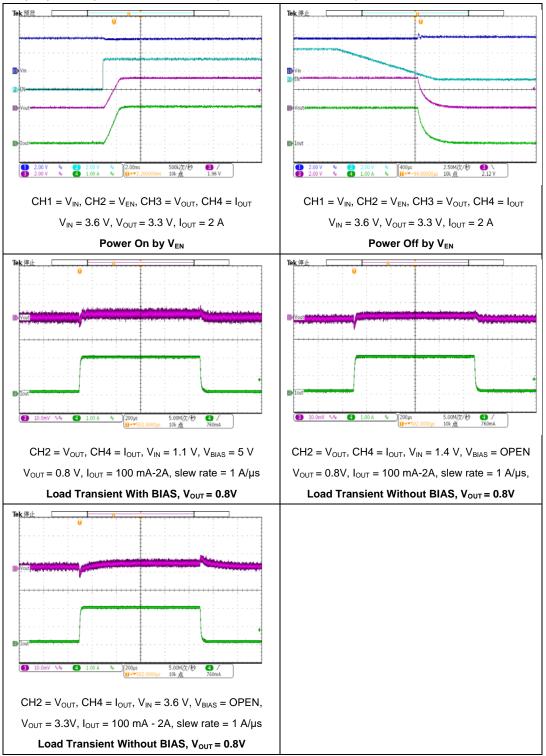

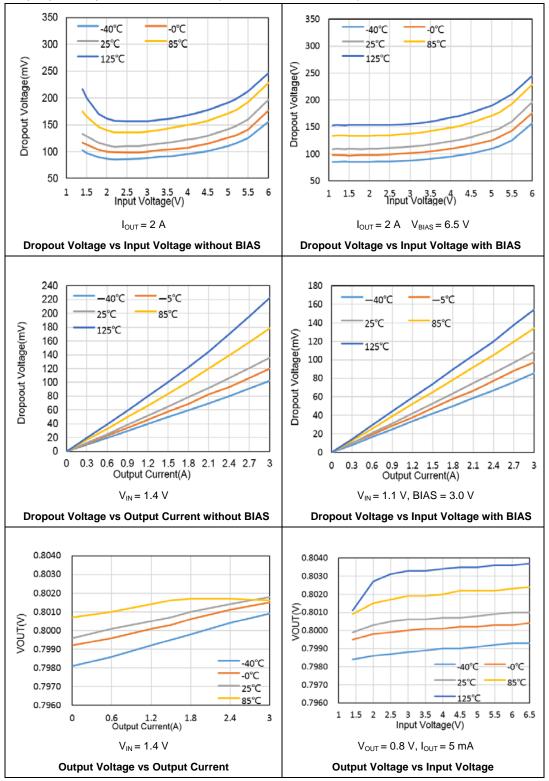

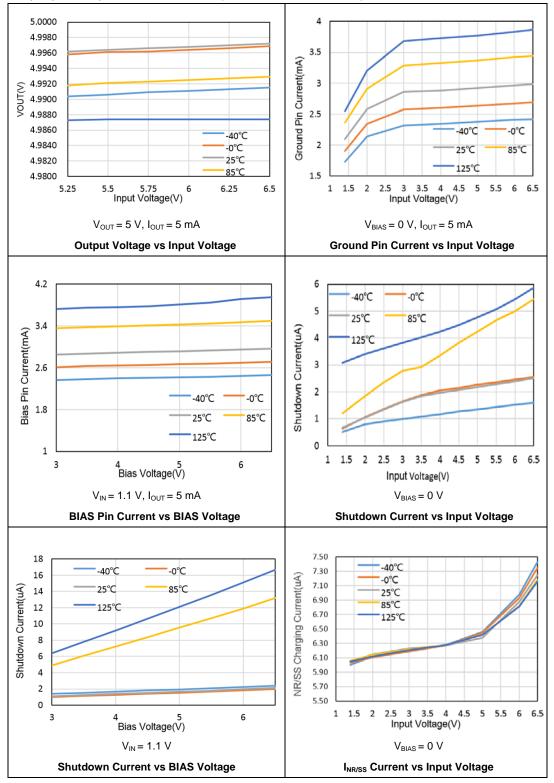

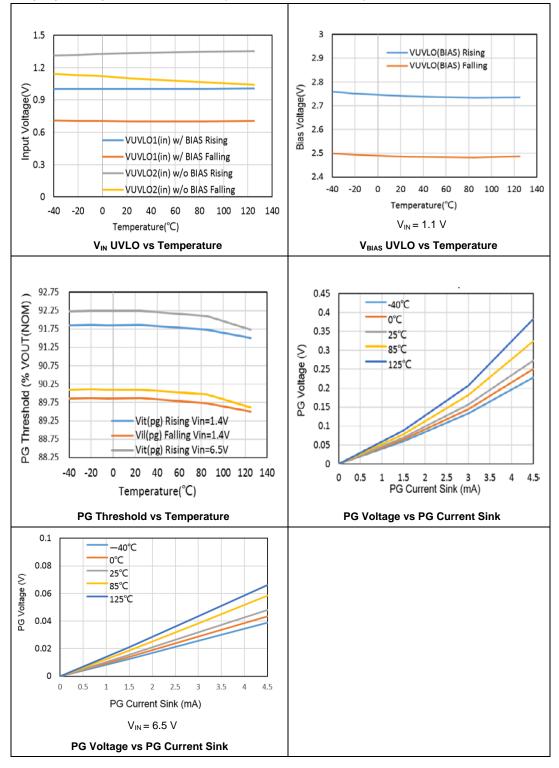

|   | 6.5   | Typical Characteristics20                                                                                                                                     |  |  |  |  |  |  |  |

| 7 | Ţ     | ypical application circuit29                                                                                                                                  |  |  |  |  |  |  |  |

| 8 |       | ayout guideline                                                                                                                                               |  |  |  |  |  |  |  |

| 9 | Р     | ackage information33                                                                                                                                          |  |  |  |  |  |  |  |

|   |       | 2                                                                                                                                                             |  |  |  |  |  |  |  |

| 9.1 | QFN20 package outline dimensions | 33 |

|-----|----------------------------------|----|

| 9.2 | Thermal characteristics          | 35 |

| 10  | Ordering information             |    |

| 11  | Revision history                 |    |

## List of Figures

| Figure 4-1 Block diagram for GD30LD1003x                                      | 8    |

|-------------------------------------------------------------------------------|------|

| Figure 4-2 GD30LD1003x QFN20 pinouts                                          | 9    |

| Figure 5-1 Typical PG Operation                                               | . 12 |

| Figure 5-2 Typical UVLO Operation                                             | . 14 |

| Figure 7-1 Typical GD30LD1003x application circuit with adjustable resistance | . 29 |

| Figure 7-2 Typical GD30LD1003x application circuit with pin-setting           | . 30 |

| Figure 8-1 Typical GD30LD1003x layout guideline                               | . 32 |

| Figure 9-1 QFN20 package outline                                              | . 33 |

| Figure 9-2 QFN20 recommend footprint                                          | . 34 |

## List of Tables

| 8  |

|----|

| 9  |

| 12 |

| 14 |

| 16 |

| 16 |

| 17 |

| 17 |

| 29 |

| 30 |

| 33 |

| 35 |

| 36 |

| 37 |

|    |

#### 1 Features

- Input Voltage Range

- With BIAS: 1.1 V to 6.5 V

- Without BIAS: 1.4 V to 6.5 V

- Output Voltage Range

- 0.8 V to 5.2 V, Set by a Resistor Divider

- 0.8 V to 3.95 V, Pin-Setting, No External Resistor

- Accurate Output Voltage Accuracy: 1%, Over Line, Load and Temperature

- Ultra Low Dropout Voltage: Maximum 125 mV at 2 A with BIAS

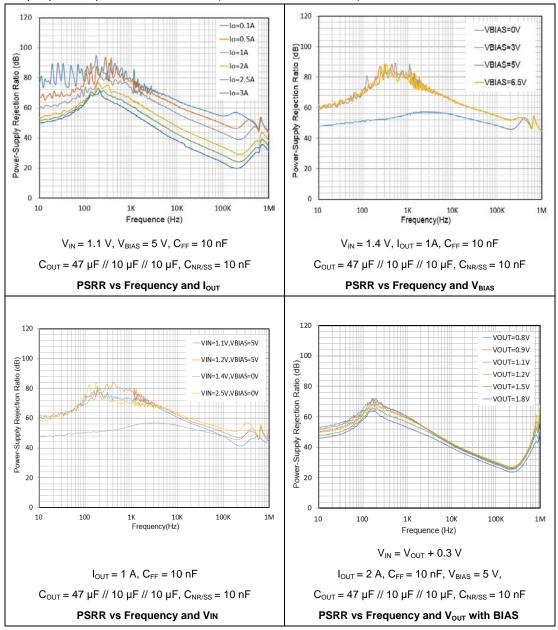

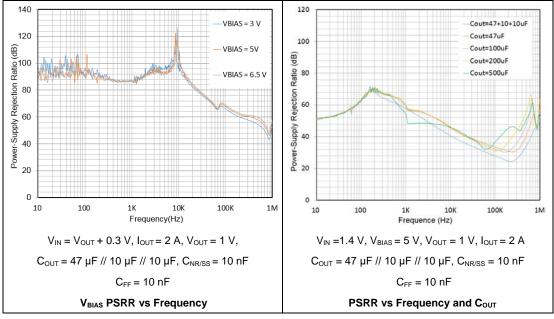

- Ultra High PSRR: 39 dB at 500 KHz

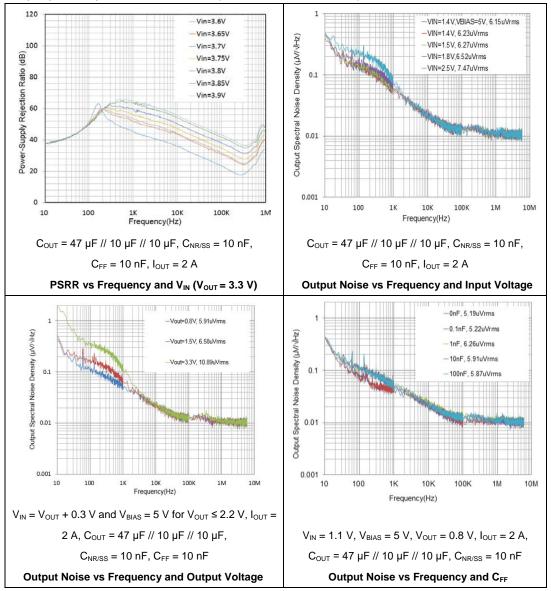

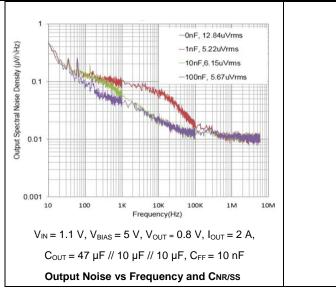

- Excellent Noise Immunity

- 5.9 uVRMS at 0.8 V Output

- 9.8 uVRMS at 5 V Output

- Enable Function

- Programmable Soft-Start

- Power-Good Indicator Function

## 2 Applications

- Wireless Infrastructure: 5G AAU, 4G RRU....

- Telecom/Networking Cards

- Industrial Application

## 3 General description

The GD30LD1003x is a high-current, low-noise, high accuracy, low-dropout linear regulator (LDO) capable of sourcing 2A with extreme low dropout (max, 125 mV).

The device output voltage is pin-setting from 0.8V to 3.95V and adjustable from 0.8V to 5.2V using the external resistor divider. The device supports input supply voltage as low to 1.1V with BIAS and as low to 1.4V without BIAS.

The low noise, high PSRR and high output current capability makes the GD30LD1003xx ideal to power noise-sensitive devices such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and RF components. With very high accuracy, remote sensing, and soft-start capabilities to reduce inrush current, the GD30LD1003x is ideal for powering digital loads such as FPGAs, DSPs, and ASICs.

The external enable control and power good indicator function makes the control sequence easier. The output noise immunity is enhanced by adding external bypass capacitor on

•

## GD30LD1003x Datasheet

NR/SS pin. The device is fully specified over the temperature range of  $T_J = -40^{\circ}$ C to 125°C and is offered in a QFN20 5.0x5.0mm package.

## 4 Device overview

### 4.1 Device information

#### Table 4-1 Device information for GD30LD1003x

| Part Number Package |                | Function           | Description                    |  |

|---------------------|----------------|--------------------|--------------------------------|--|

| GD30LD1003x         | QFN20(5.0X5.0) | With EN enable pin | 2A High accuracy and Low noise |  |

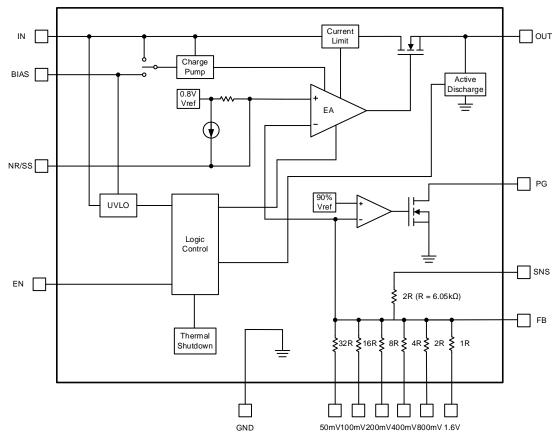

### 4.2 Block diagram

#### Figure 4-1 Block diagram for GD30LD1003x

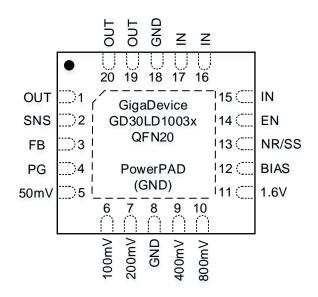

### 4.3 Pinout and pin assignment

#### Figure 4-2 GD30LD1003x QFN20 pinouts

### 4.4 Pin definitions

#### Table 4-2 GD30LD1003x QFN20 pin definitions

| Pin Name                                                       | Pins      | Pin<br>Type                                                                                                                                                                                                                                       | Functions description                                                                                                                                                                                          |

|----------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT                                                            | 1, 19, 20 | 0                                                                                                                                                                                                                                                 | <b>LDO output pins</b> . The larger ceramic capacitor (22uF or greater) is stable. Place the output capacitor as close to the device as possible. Minimize the impedance between V <sub>OUT</sub> pin to load. |

| SNS                                                            | 2         | I                                                                                                                                                                                                                                                 | <b>Output voltage sense input pin</b> . Connect this pin only if using the configuration without external resistors. Keep SNS pin floating if the V <sub>OUT</sub> voltage is set by external resistor.        |

| FB                                                             | 3         | Ι                                                                                                                                                                                                                                                 | <b>Feedback voltage input</b> . This pin is used to set the desired output voltage via an external resistive divider. The feedback reference voltage is 0.8V typically.                                        |

| PG 4 O high when the output volta is pulled to ground when the |           | <b>Power good indicator output</b> . An open-drain output and active high when the output voltage reaches 89% of the target. The pin is pulled to ground when the output voltage is lower than its specified threshold, EN shutdown, OCP and OTP. |                                                                                                                                                                                                                |

| [5,6,7,9,10,11] O [ 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5        |           | Output voltage setting pins. Connect these pins to ground or leave floating. Connecting these pins to ground increases the                                                                                                                        |                                                                                                                                                                                                                |

| Pin Name                                                                                                                                                                                                                                                                                                                                         | Pins                   | Pin<br>Type                                                                                                                                                                                                                                                                                                                                                                                             | Functions description                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 800mV,1.6V                                                                                                                                                                                                                                                                                                                                       |                        |                                                                                                                                                                                                                                                                                                                                                                                                         | output voltage by the value of the pin name; multiple pins can be simultaneously connected to GND to select the desired output voltage. Leave these pins floating (open) if the $V_{OUT}$ voltage is set by external resistor.                                                                                                                                                                                                     |

| GND                                                                                                                                                                                                                                                                                                                                              | 8,18,21<br>Thermal pad | G                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Ground</b> . The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                                                                                                                                |

| BIAS                                                                                                                                                                                                                                                                                                                                             | 12                     | I                                                                                                                                                                                                                                                                                                                                                                                                       | <b>BIAS supply voltage</b> . This pin enables the use of low-input voltage, low-output (LILO) voltage conditions (that is, $V_{IN} = 1.2V$ , $V_{OUT} = 1V$ ) to reduce power dissipation across the die. The use of a BIAS voltage improves dc and ac performance for $V_{IN} \le 2.2$ V. A 1µF capacitor or larger must be connected between this pin and ground. If not used, this pin must be left floating or tied to ground. |

| NR/SS                                                                                                                                                                                                                                                                                                                                            | 13                     | I                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Noise-reduction and soft-start pin</b> . Decouple this pin to GND with an external capacitor $C_{NR/SS}$ can not only reduce output noise to very low levels but also slow down the rising of $V_{OUT}$ , providing a soft-start behavior. For low noise applications, a 10nF to 100nF $C_{NR/SS}$ is suggested.                                                                                                                |

| EN       14       I       the regulator, and driving this pin low p         The device can have V <sub>IN</sub> and V <sub>EN</sub> seque       causing damage to the device. Howeve         function to work as intended, certain se       applied. Enabling the device after V <sub>IN</sub> is         Supply input. A general 10uF or larger |                        | <b>Enable control input</b> . Connecting this pin to logic high enables the regulator, and driving this pin low puts it into shutdown mode. The device can have $V_{IN}$ and $V_{EN}$ sequenced in any order without causing damage to the device. However, for the soft-start function to work as intended, certain sequencing rules must be applied. Enabling the device after $V_{IN}$ is preferred. |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                  |                        | I                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Supply input</b> . A general 10uF or larger ceramic capacitor should be placed as close as possible to this pin for better noise rejection.                                                                                                                                                                                                                                                                                     |

#### Notes:

1. Type: I = input, O = output, I/O = input or output, P = power, G = Ground.

## 5 Functional description

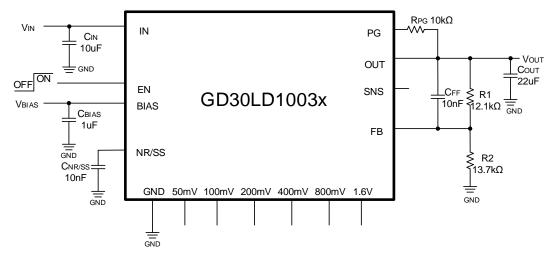

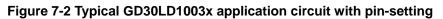

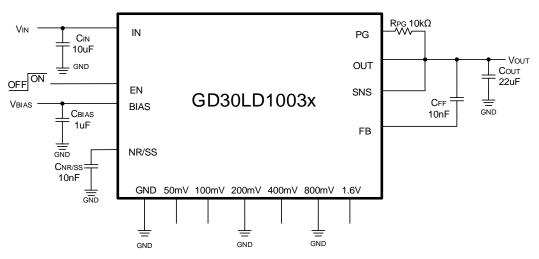

#### 5.1 Output Voltage Setting

The output voltage of the GD30LD1003x can be set by external resistors or by using the output voltage setting pins (50mV, 100mV, 200mV, 400mV, 800mV and 1.6V) to achieve different output targets. By using external resistors, the output voltage is determined by the values of R1 and R2 as shown in Table 7-1. The values of R1 and R2 can be calculated for any voltage value using the following formula:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_1}{R_2}\right)$$

The GD30LD1003x can also short pins 5, 6, 7, 9, 10, and 11 to ground and program the regulated output voltage level without external resistors after the SNS pin is connected to the  $V_{OUT}$ . Pins 5, 6, 7, 9, 10, and 11 are connected with internal resistor pairs. Each pin is either connected to ground (active) or left open (floating). Voltage programming is set as the sum of the internal reference voltage ( $V_{FB} = 0.8V$ ) plus the accumulated sum of the respective voltages assigned to each active pin as illustrated in Table 7-2.

$$V_{OUT} = V_{FB} + V_{PIN-SET}$$

#### 5.2 Recommended device selection

#### 5.2.1 CIN and COUT Selection

The GD30LD1003x is designed to support low-series resistance (ESR) ceramic capacitors. It is recommended to use ceramic capacitors with X7R, X5R, and C0G-rated ceramic capacitors to get good capacitive stability across different temperatures.

However, the capacitance of ceramic capacitors varies with operating voltage and temperature, and the design engineer must be aware of these characteristics. Ceramic capacitors are usually recommended to be derated by 50%. A  $22\mu$ F or greater output ceramic capacitor is suggested to ensure stability. Input capacitance is selected to minimize transient input drop during load current steps. For general applications, an input capacitor of at least  $10\mu$ F is highly recommended for minimal input impedance. If the trace inductance between the GD30LD1003x input pin and power supply is high, a fast load transient can cause V<sub>IN</sub> voltage level ringing above the absolute maximum voltage rating which damages the device. Adding more input capacitors is available to restrict the ringing and keep it below the device absolute maximum ratings.

#### 5.2.2 Feed-Forward Capacitor (CFF)

Although a feed-forward capacitor (CFF) from the FB pin to the OUT pin is not required to

achieve stability, a 10nF external feed-forward capacitor optimizes the transient, noise, and PSRR performance. A higher capacitance  $C_{FF}$  can be used; however, the start-up time is longer and the power-good signal can incorrectly indicate that the output voltage is settled.

### 5.3 Low-Noise, High-RSRR Output

The GD30LD1003x includes a low-noise reference and error amplifier ensuring minimal noise during operation. The NR/SS capacitor ( $C_{NR/SS}$ ) and feed-forward capacitor ( $C_{FF}$ ) are the easiest way to reduce device noise.  $C_{NR/SS}$  filters the noise from the reference and CFF filters the noise from the error amplifier. The noise contribution from the charge pump is minimal. The overall noise of the system at low output voltages can be reduced by using a bias rail because this rail provides more headroom for internal circuitry.

The high power-supply rejection ratio (PSRR) of the GD30LD1003x ensures minimal coupling of input supply noise to the output. The PSRR performance is primarily results from a high-bandwidth, high-gain error amplifier and an innovative circuit to boost the PSRR between 200kHz and 1MHz.

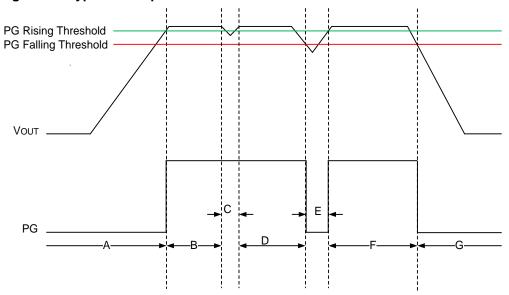

### 5.4 Power-Good Function

The PG circuit monitors the voltage at the feedback pin to indicate the status of the output voltage. The PG circuit asserts whenever FB,  $V_{IN}$ , or EN are below their thresholds. The PG operation versus the output voltage is shown in Figure 5-1, ch is described by Table 5-1.

#### Figure 5-1 Typical PG Operation

#### Table 5-1 Typical PG Operation Description

| Region EVENT |         | PG STATUS | FB VOLTAGE                          |  |

|--------------|---------|-----------|-------------------------------------|--|

| А            | Turn on | 0         | $V_{FB} < V_{IT(PG)} + V_{HYS(PG)}$ |  |

| В | Regulation         | Hi-Z |                          |

|---|--------------------|------|--------------------------|

| С | Output voltage dip | Hi-Z | $V_{FB} \geq V_{IT(PG)}$ |

| D | Regulation         | Hi-Z |                          |

| E | Output voltage dip | 0    | Vfb < Vit(pg)            |

| F | Regulation         | Hi-Z | $V_{FB} \geq V_{IT(PG)}$ |

| G | G Turnoff          |      | Vfb < Vit(pg)            |

The PG pin is open-drain, and connecting a pullup resistor to an external supply enables others devices to receive Power Good as a logic signal that can be used for sequencing. Make sure that the external pullup supply voltage results in a valid logic signal for the receiving device or devices.

To ensure proper operation of the PG circuit, the pullup resistor value must be from  $10k\Omega$  and  $100k\Omega$ . The lower limit of  $10k\Omega$  results from the maximum pulldown strength of the PG transistor, and the upper limit of  $100k\Omega$  results from the maximum leakage current at the PG node. If the pullup resistor is outside of this range, then the PG signal may not read a valid digital logic level.

### 5.5 Soft-Start Function

The GD30LD1003x is designed for a programmable, monotonic soft-start time during the output rising, which can be achieved via an external capacitor ( $C_{NR/SS}$ ) on NR/SS pin. Using an external  $C_{NR/SS}$  is recommended for general application, it is not only for the in-rush current minimization but also helps reduce the noise component from the internal reference. During the monotonic start-up procedure, the error amplifier of the GD30LD1003x tracks the voltage ramp of the external soft-start capacitor ( $C_{NR/SS}$ ) until the voltage approaches the internal reference 0.8V.

The soft-start ramp time can be calculated with equation, which depends on the soft-start charging current ( $I_{NR/SS}$ ), the soft-start capacitance ( $C_{NR/SS}$ ), and the internal reference 0.8V ( $V_{FB}$ ).

$$\mathbf{t}_{\text{SS}} = \left( \mathbf{V}_{\text{NR/SS}} \times \mathbf{C}_{\text{NR/SS}} \right) / \mathbf{I}_{\text{NR/SS}}$$

For noise-reduction, CNR/SS in conjunction with an internal noise-reduction resistor forms a low-pass filter (LPF) and filters out the noise from the internal bandgap reference before being amplified via the error amplifier, thus reducing the total device noise floor.

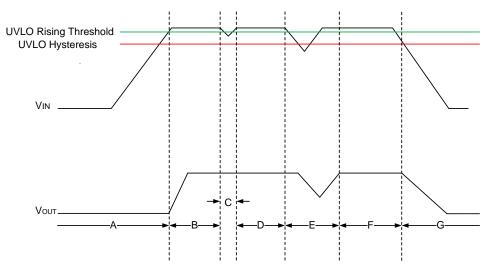

### 5.6 Undervoltage Lockout (UVLO)

The UVLO circuits ensure that the device stays disabled before its input or bias supplies reach the minimum operational voltage range, and ensures that the device properly shuts down when either the input or bias supply collapses. Figure 5-1 and Table 5-2 explain one of the UVLO circuits being triggered to various input voltage events, assuming  $V_{\text{EN}} > V_{\text{IH(EN)}}$ .

#### Figure 5-2 Typical UVLO Operation

#### Table 5-2 Typical UVLO Operation Description

| Region | EVENT                                                                                                      | VOUT<br>STATUS | COMMENT                                                                                                                                                                                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А      | Turn on,<br>$V_{IN} \ge V_{UVLO_1,2(IN)}$ and<br>$V_{BIAS} \ge V_{UVLO(BIAS)}$                             | Off            | Startup                                                                                                                                                                                                                                                                                                   |

| В      | Regulation                                                                                                 | On             | Regulates to target Vout                                                                                                                                                                                                                                                                                  |

| С      | Brown out,<br>$V_{IN} \ge V_{UVLO_{-1,2}(IN)} - V_{HYS_{-1,2}(IN)}$<br>or $V_{UVLO(BIAS)} - V_{HYS(BIAS)}$ | On             | The output can fall out of<br>regulation but the device is still<br>enabled                                                                                                                                                                                                                               |

| D      | Regulation                                                                                                 | On             | Regulates to target Vout                                                                                                                                                                                                                                                                                  |

| E      | Brownout<br>Vin < Vuvlo_1,2(in) - Vhys_1,2(in)<br>or Vbias≥Vuvlo(bias) - Vhys(bias)                        | Off            | The device is disabled and the<br>output falls because of the load<br>and active discharge circuit. The<br>device is reenabled when the<br>UVLO fault is removed when<br>either the IN or BIAS UVLO rising<br>threshold is reached by the input<br>or bias voltage and a normal<br>start-up then follows. |

| F | Regulation                                                                           | On  | Regulates to target Vout                                           |

|---|--------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|

| G | Turnoff,<br>Vin < Vuvlo_1,2(in) –Vhys_1,2(in)<br>or Vbias < Vuvlo(bias) – Vhys(bias) | Off | The output falls because of the load and active discharge circuit. |

Similar to many other LDOs with this feature, the UVLO circuits take a few microseconds to fully assert. During this time, a downward line transient below approximately 0.8V causes the UVLO to assert for a short time; however, the UVLO circuits do not have enough stored energy to fully discharge the internal circuits inside of the device. When the UVLO circuits are not given enough time to fully discharge the internal nodes, the outputs are not fully disabled.

The effect of the downward line transient can be mitigated by using a larger input capacitor to increase the fall time of the input supply when operating near the minimum V<sub>IN</sub>.

### 5.7 Power Dissipation (P<sub>D</sub>)

Circuit reliability demands that proper consideration is given to device power dissipation, location of the circuit on the printed circuit board (PCB), and correct sizing of the thermal plane. The PCB area around the regulator must be as free as possible of other heat-generating devices that cause added thermal stresses.

Power dissipation in the regulator depends on the input-to-output voltage difference and load conditions.

$$\textbf{P}_{D} = \left( \textbf{V}_{\text{IN}} - \textbf{V}_{\text{OUT}} \right) \times \textbf{I}_{\text{OUT}} + \textbf{V}_{\text{IN}} \times \textbf{I}_{\text{GND}}$$

$V_{IN} \times I_{GND}$  represents the static power consumption of the LDO, the value is relatively small and can be ignored. An important note is that power dissipation can be minimized, and thus greater efficiency achieved, by proper selection of the system voltage rails. Proper selection allows the minimum input-to-output voltage differential to be obtained. The low dropout of the device allows for maximum efficiency across a wide range of output voltages.

The main heat conduction path for the device is through the thermal pad on the package. As such, the thermal pad must be soldered to a copper pad area under the device. This pad area contains an array of plated vias that conduct heat to any inner plane areas or to a bottom-side copper plane.

The maximum power dissipation determines the maximum allowable junction temperature  $(T_J)$  for the device. Power dissipation and junction temperature are most often related by the junction-to-ambient thermal resistance ( $\theta_{JA}$ ) of the combined PCB, device package, and the temperature of the ambient air ( $T_A$ ).

$$\begin{split} T_{J} &= T_{A} + \theta_{JA} \times P_{D} \\ I_{OUT} &= \left(T_{J} - T_{A}\right) / \left[\theta_{JA} \times \left(V_{IN} - V_{OUT}\right)\right] \end{split}$$

## 6 Electrical characteristics

#### 6.1 Absolute maximum ratings

The maximum ratings are the limits to which the device can be subjected without permanently damaging the device. Note that the device is not guaranteed to operate properly at the maximum ratings. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

Table 6-1 Absolute maximum ratings

| Symbol           | Parameter                      | Min        | Max        | Unit |  |  |

|------------------|--------------------------------|------------|------------|------|--|--|

| Voltago          | IN, BIAS, PG, EN, OUT          | -0.3       | 7.0        | V    |  |  |

| Voltage          | NR/SS, FB                      | -0.3       | 3.6        | V    |  |  |

|                  |                                | Internally | Internally | А    |  |  |

| Current          | OUT                            | limited    | limited    |      |  |  |

|                  | PG(sink current into device)   | _          | 5          | mA   |  |  |

|                  | Thermal characteristics        |            |            |      |  |  |

| TJ               | Operating junction temperature | -55        | 150        | °C   |  |  |

| T <sub>stg</sub> | Storage temperature            | -65        | 150        | °C   |  |  |

### 6.2 Recommended Operating Conditions

| Symbol           | Parameter                    | Min | Тур | Max | Unit |

|------------------|------------------------------|-----|-----|-----|------|

| Vin              | Input voltage range          | 1.1 |     | 6.5 | V    |

| VBIAS            | Bias supply voltage range    | 3.0 |     | 6.5 | V    |

| V <sub>OUT</sub> | Output voltage range         | 0.8 | _   | 5.2 | V    |

| V <sub>EN</sub>  | Enable Voltage range         | 0   | _   | Vin | V    |

| IOUT             | Output current               | 0   | _   | 2   | A    |

| CIN              | Input capacitor              | _   | 10  | _   | uF   |

| Соит             | Output capacitor             | _   | 22  | _   | uF   |

| Rpg              | Power-good pullup resistance | 10  | _   | 100 | kΩ   |

#### **Table 6-2 Recommended Operating Conditions**

| Symbol             | Parameter                           | Min                         | Тур  | Max | Unit |

|--------------------|-------------------------------------|-----------------------------|------|-----|------|

| C <sub>NR/SS</sub> | NR/SS capacitor                     | _                           | 10   | —   | nF   |

| Cff                | Feed-forward capacitor              | Feed-forward capacitor — 10 |      | _   | nF   |

| R1                 | Adjustable resistance in FB         |                             | 12.1 | _   | kΩ   |

| R <sub>2</sub>     | Adjustable resistance in FB network | resistance in FB            |      | 160 | kΩ   |

| TJ                 | Operating junction temperature      | -40                         |      | 125 | °C   |

### 6.3 Electrical sensitivity

The device is strained in order to determine its performance in terms of electrical sensitivity. Electrostatic discharges (ESD) are applied directly to the pins of the sample.

| Symbol    | Parameter                     | Conditions              | Value  | Unit |  |  |

|-----------|-------------------------------|-------------------------|--------|------|--|--|

| M         | Electrostatic discharge       | T <sub>A</sub> = 25 °C; | . 2000 | V    |  |  |

| Vesd(HBM) | voltage (human body model)    | JS-001-2017             | ±2000  | v    |  |  |

| V         | Electrostatic discharge       | T <sub>A</sub> = 25 °C; | .500   | V    |  |  |

| VESD(CDM) | voltage (charge device model) | JS-002-2018             | ±500   | V    |  |  |

**Table 6-3 Electrostatic Discharge characteristics**

### 6.4 Electrical Specifications

Over operating temperature range ( $T_J = -40^{\circ}C$  to 125°C), Typical values are at  $T_J = 25^{\circ}C$ . V<sub>IN</sub> = 1.4 V or V<sub>IN</sub> = V<sub>OUT (TARGET)</sub> + 0.4 V, V<sub>BIAS</sub>=OPEN, V<sub>OUT (TARGET)</sub> = 0.8 V, V<sub>OUT</sub> connected to 50  $\Omega$  to GND, V<sub>EN</sub> = 1.1 V, C<sub>IN</sub> = 10  $\mu$ F, C<sub>OUT</sub> = 22  $\mu$ F, C<sub>NR/SS</sub> = 0 nF, C<sub>FF</sub> = 0 nF, and PG pin pulled up to OUT with 100 k $\Omega$ , unless otherwise noted.

| Symbol                | Parameter                | Conditions                                            | Min | Тур  | Max   | Unit |

|-----------------------|--------------------------|-------------------------------------------------------|-----|------|-------|------|

| Vin                   | Input Range              | -                                                     | 1.1 | _    | 6.5   | V    |

| VBIAS                 | BIAS Range               | V <sub>IN</sub> = 1.1 V                               | 3.0 |      | 6.5   | V    |

| Vfb                   | Feedback<br>Voltage      | —                                                     | _   | 0.8  | _     | V    |

| V <sub>NR/SS</sub>    | NR/SS pin<br>Voltage     | _                                                     | _   | 0.8  | _     | V    |

| Vuvlo1(IN)            | UVLO1 with<br>BIAS       | $V_{\text{IN}}$ rising with $V_{\text{BIAS}}$ = 3.0 V | _   | 0.93 | 1.085 | V    |

| V <sub>HYS1(IN)</sub> | UVLO1<br>hysteresis With | $V_{BIAS} = 3.0 V$                                    | _   | 240  | _     | mV   |

#### **Table 6-4 Electrical characteristics**

| Cumple of                  | DI Parameter Conditions Min |                                                                                                 |      |       |      |      |

|----------------------------|-----------------------------|-------------------------------------------------------------------------------------------------|------|-------|------|------|

| Symbol                     | Parameter                   | Conditions                                                                                      | Min  | Тур   | Max  | Unit |

|                            | BIAS                        |                                                                                                 |      |       |      |      |

| VUVLO2(IN)                 | UVLO2 without               | V <sub>IN</sub> rising                                                                          | _    | 1.33  | 1.39 | V    |

| ()                         | BIAS                        |                                                                                                 |      |       |      |      |

|                            | UVLO2                       |                                                                                                 |      |       |      |      |

| V <sub>HYS2</sub> (IN)     | hysteresis                  |                                                                                                 |      | 230   | —    | mV   |

|                            | without BIAS                |                                                                                                 |      |       |      |      |

| V <sub>UVLO(BIAS)</sub>    | UVLO(BIAS)                  | $V_{BIAS}$ rising, $V_{IN}$ = 1.1 V                                                             |      | 2.72  | 2.9  | V    |

|                            | UVLO(BIAS)                  |                                                                                                 |      |       |      |      |

| VHYS(BIAS)                 | hysteresis With             | $V_{IN} = 1.1 V$                                                                                |      | 250   | —    | mV   |

|                            | BIAS                        |                                                                                                 |      |       |      |      |

|                            |                             | Using Voltage setting pins (50                                                                  |      |       | 0.05 |      |

|                            |                             | mV, 100 mV, 200 mV, 400 mV,                                                                     | 0.8  |       | 3.95 | V    |

|                            | Output Voltage              | 800 mV and 1.6 V)                                                                               | -1%  |       | +1%  |      |

| Vout                       | Range                       |                                                                                                 | 0.8  |       | 5.2  |      |

|                            |                             | Using external resistors                                                                        | -1%  |       | +1%  | V    |

|                            |                             | $V_{IN} = V_{OUT} + 0.3 V,$                                                                     |      |       |      |      |

|                            | Output Accuracy             | 0.8 V ≤ V <sub>OUT</sub> ≤ 5.2 V                                                                | -1   |       | 1    | %    |

| ∆Vout/                     |                             | loυτ = 5 mA,                                                                                    |      | — 0.1 | _    |      |

| <br>∆Vin                   | Line Regulation             | 1.4 V ≤ V <sub>IN</sub> ≤ 6.5 V                                                                 | —    |       |      | mV/V |

| ∆Vout/                     |                             |                                                                                                 |      |       |      |      |

| ∆I <sub>о∪т</sub>          | Load Regulation             | 5 mA ≤ I <sub>OUT</sub> ≤ 2 A                                                                   | —    | 0.3   | —    | mV/A |

|                            |                             | V <sub>IN</sub> = 1.4 V, I <sub>OUT</sub> = 2 A,                                                |      |       |      |      |

|                            |                             | $V_{FB} = 0.8 V - 3\%$                                                                          |      |       | 200  | mV   |

|                            |                             | VIN = 5.4 V, IOUT = 2 A,                                                                        |      |       |      |      |

| Vdrop                      | Dropout Voltage             | $V_{FB} = 0.8 V - 3\%$                                                                          |      |       | 200  | mV   |

|                            |                             | $V_{\rm FB} = 0.0 V = 370$<br>$V_{\rm IN} = 1.1 \text{ V}, \text{ V}_{\rm BIAS} = 5 \text{ V},$ |      |       |      |      |

|                            |                             |                                                                                                 |      | —     | 125  | mV   |

|                            | Output Current              | $I_{OUT} = 2 \text{ A}, \text{ V}_{FB} = 0.8 \text{ V} - 3\%$                                   |      |       |      |      |

| ILIM                       | Output Current              | $V_{OUT} = 90\% * V_{OUT(TARGET)}$                                                              |      | 3.0   | —    | Α    |

|                            | Limit                       | $V_{IN} = V_{OUT(TARGET)} + 400 \text{ mV}$                                                     |      |       |      |      |

| lsc                        | Short-Circuit               | $R_{LOAD} = 20 m\Omega$                                                                         |      | 1     | _    | А    |

|                            | Current Limit               |                                                                                                 |      |       |      |      |

|                            |                             | Vin = 6.5 V, I <sub>OUT</sub> = 5 mA                                                            |      | 3.0   | 4.2  | mA   |

| Ignd                       | Ground Pin                  | Vin = 1.4 V, I <sub>OUT</sub> = 2 A                                                             |      | 4.2   | 5.5  | mA   |

|                            | Current                     | Shutdown, PG = OPEN,                                                                            | _    |       | 25   | uA   |

|                            |                             | $V_{IN} = 6.5 \text{ V}, V_{EN} = 0.5 \text{ V}$                                                |      |       |      |      |

| IBIAS                      | BIAS Pin                    | V <sub>IN</sub> = 1.1 V, V <sub>BIAS</sub> = 6.5 V,                                             |      | 3.0   | 4.2  | mA   |

| -                          | Current                     | Vout = 0.8 V, Iout = 2 A                                                                        |      |       |      |      |

| I <sub>EN</sub>            | EN Pin Current              | $V_{IN} = 6.5 \text{ V},  V_{EN} = 0 \text{ V}$                                                 | -0.1 | _     | 0.1  | uA   |

|                            |                             | and 6.5 V                                                                                       |      |       |      |      |

| V <sub>EN_H</sub>          | EN Pin                      | _                                                                                               | 1.1  | _     | 6.5  | V    |

| ¥ EIN_H                    | High-Level                  |                                                                                                 |      |       | 0.0  | v    |

| $V_{\text{EN}_{\text{L}}}$ | EN Pin                      |                                                                                                 | 0    |       | 0.5  | V    |

|                     | _                | GD30                                                                                               |                                |                   |                   |                   |                   |  |  |  |  |

|---------------------|------------------|----------------------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|-------------------|-------------------|--|--|--|--|

| Symbol              | Parameter        | Conditio                                                                                           | ns                             | Min               | Тур               | Max               | Unit              |  |  |  |  |

|                     | Low-Level        |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

| VIT(PG)             | PG Pin           | For falling                                                                                        | Vout                           | 83%               | 88%               | 93%               | V                 |  |  |  |  |

| VII(FG)             | Threshold        | For falling Vout                                                                                   |                                | *V <sub>OUT</sub> | *V <sub>оит</sub> | *V <sub>оит</sub> | •                 |  |  |  |  |

| V <sub>HYS_PG</sub> | PG Pin           | For rising Vout                                                                                    |                                |                   | 3%                |                   | v                 |  |  |  |  |

| VHYS_PG             | Hysteresis       |                                                                                                    |                                |                   | *Vouт             |                   | v                 |  |  |  |  |

|                     | PG Pin           |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

| $V_{PG_L}$          | Low-Level        | $V_{OUT} < V_{IT(PG)}, I_{P}$                                                                      | <sub>G</sub> = -1 mA           |                   | —                 | 0.1               | V                 |  |  |  |  |

|                     | output Voltage   |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

|                     | PG Pin           |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

| IPG_LK              | Low-leakage      | Vout > Vit(pg), Vi                                                                                 | ⊳g = 6.5 V                     |                   | _                 | 1                 | uA                |  |  |  |  |

|                     | Current          |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

|                     | NR/SS Pin        |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

| INR/SS              | Charging         | VIN = GND, VIN                                                                                     | = 6.5 V                        | 4                 | 7.2               | 9                 | uA                |  |  |  |  |

|                     | Current          |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

|                     | FB Pin leakage   |                                                                                                    |                                |                   |                   |                   |                   |  |  |  |  |

| I <sub>FB</sub>     | Current          | V <sub>IN</sub> = 6.5                                                                              | V                              | -100              | —                 | 100               | nA                |  |  |  |  |

|                     | ounon            |                                                                                                    | f =10 KHz,                     |                   |                   |                   |                   |  |  |  |  |

|                     |                  |                                                                                                    | Vout=0.8 V                     |                   | 42                |                   | dB                |  |  |  |  |

|                     |                  |                                                                                                    | $V_{BIAS} = 5 V$               |                   | 42                | _                 | uВ                |  |  |  |  |

|                     |                  |                                                                                                    | $v_{\text{BIAS}} = 5 v$<br>f = |                   |                   |                   |                   |  |  |  |  |

|                     |                  | V <sub>IN</sub> -V <sub>OUT</sub> = 0.4 V<br>I <sub>OUT</sub> = 2 A<br>C <sub>NR/SS</sub> = 100 nF |                                |                   |                   |                   |                   |  |  |  |  |

|                     |                  |                                                                                                    | 500KHz,                        |                   |                   |                   | JD                |  |  |  |  |

| 2022                | Power Supply     |                                                                                                    | V <sub>OUT</sub> = 0.8         |                   | 39                | _                 | dB                |  |  |  |  |

| PSRR                | Ripple Rejection | C <sub>FF</sub> = 10 nF                                                                            | V                              |                   |                   |                   |                   |  |  |  |  |

|                     |                  | Cout=                                                                                              | VBIAS = 5V                     |                   |                   |                   |                   |  |  |  |  |

|                     |                  | 47uF//10uF//10uF                                                                                   | f =10 KHz,                     |                   | 40                | _                 | dB                |  |  |  |  |

|                     |                  |                                                                                                    | Vout = 5 V                     |                   |                   |                   |                   |  |  |  |  |

|                     |                  |                                                                                                    | f = 500                        |                   |                   |                   |                   |  |  |  |  |

|                     |                  |                                                                                                    | KHz,                           |                   | 25                | —                 | dB                |  |  |  |  |

|                     |                  |                                                                                                    | $V_{OUT} = 5 V$                |                   |                   |                   |                   |  |  |  |  |

|                     |                  | BW = 10 Hz to                                                                                      |                                |                   |                   |                   |                   |  |  |  |  |

|                     |                  | Vin = 1.1                                                                                          | V                              |                   |                   |                   |                   |  |  |  |  |

|                     |                  | $V_{OUT} = 0.8 V, V_{E}$                                                                           | BIAS = 5 V,                    |                   | 5.9               | _                 | uV <sub>RMS</sub> |  |  |  |  |

|                     |                  | I <sub>OUT</sub> = 2                                                                               | Α,                             |                   | 0.0               |                   |                   |  |  |  |  |

| V <sub>N</sub>      | Output Noise     | $C_{NR/SS} = 100 \text{ nF}, 0$                                                                    | C <sub>FF</sub> = 10 nF        |                   |                   |                   |                   |  |  |  |  |

| ۷N                  | Voltage          | C <sub>OUT</sub> = 47 uF//10                                                                       | uF//10 uF                      |                   |                   |                   |                   |  |  |  |  |

|                     |                  | BW = 10 Hz to                                                                                      | 100 KHz,                       |                   |                   |                   |                   |  |  |  |  |

|                     |                  | Vout= 5.0 V, Io                                                                                    | υт <b>=</b> 2 A,               |                   | 9.8               |                   | uV <sub>RMS</sub> |  |  |  |  |

|                     |                  | $C_{NR/SS} = 100 \text{ nF}, 0$                                                                    | C <sub>FF</sub> = 10 nF        |                   | 9.0               |                   | UVRMS             |  |  |  |  |

|                     |                  | C <sub>OUT</sub> = 47 uF//10                                                                       | uF//10 uF                      |                   |                   |                   |                   |  |  |  |  |

|                     | Thermal          | Shut down, tem                                                                                     | perature                       |                   | 400               |                   | • •               |  |  |  |  |

| T <sub>SD</sub>     | Shutdown         | increasir                                                                                          | ng                             | _                 | 160               |                   | °C                |  |  |  |  |

|                     | Threshold        | Reset, temperature                                                                                 | e increasing                   | _                 | 140               |                   | °C                |  |  |  |  |

$T_A = 25^{\circ}C$ ,  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(NOM)} + 0.4$  V (whichever is greater),  $V_{BIAS} = OPEN$ ,  $V_{OUT(NOM)} = 0.8$  V,  $V_{EN} = 1.1$  V,  $C_{OUT} = 47$  uF // 10 µF// 10 µF,  $C_{NR/SS} = 10$  nF,  $C_{FF} = 10$  nF, and PG pin pulled up to  $V_{IN}$  with 100 k $\Omega$  (unless otherwise noted).

$T_A = 25^{\circ}C, V_{IN} = 1.4 \text{ V or } V_{IN} = V_{OUT(NOM)} + 0.4 \text{ V (whichever is greater)}, V_{BIAS} = OPEN, V_{OUT(NOM)} = 0.8 \text{ V}, V_{EN} = 1.1 \text{ V}, C_{OUT} = 47 \text{ uF } // 10 \text{ µF/} 10 \text{ µF}, C_{NR/SS} = 10 \text{ nF}, C_{FF} = 10 \text{ nF}, \text{ and PG pin pulled up to } V_{IN} \text{ with } 100 \text{ k}\Omega \text{ (unless otherwise noted)}.$

$T_{A} = 25^{\circ}C, V_{IN} = 1.4 \text{ V or } V_{IN} = V_{OUT(NOM)} + 0.4 \text{ V (whichever is greater)}, V_{BIAS} = OPEN, V_{OUT(NOM)} = 0.8 \text{ V}, V_{EN} = 1.1 \text{ V}, C_{OUT} = 47 \text{ uF } // 10 \text{ µF/} 10 \text{ µF}, C_{NR/SS} = 10 \text{ nF}, C_{FF} = 10 \text{ nF}, \text{ and PG pin pulled up to } V_{IN} \text{ with } 100 \text{ k}\Omega \text{ (unless otherwise noted)}.$

$T_{A} = 25^{\circ}C, V_{IN} = 1.4 \text{ V or } V_{IN} = V_{OUT(NOM)} + 0.4 \text{ V (whichever is greater)}, V_{BIAS} = OPEN, V_{OUT(NOM)} = 0.8 \text{ V}, V_{EN} = 1.1 \text{ V}, C_{OUT} = 47 \text{ uF } // 10 \text{ µF} // 10 \text{ µF}, C_{NR/SS} = 10 \text{ nF}, C_{FF} = 10 \text{ nF}, \text{ and PG pin pulled up to } V_{IN} \text{ with } 100 \text{ k}\Omega \text{ (unless otherwise noted)}.$

$T_{A} = 25^{\circ}C, V_{IN} = 1.4 \text{ V or } V_{IN} = V_{OUT(NOM)} + 0.4 \text{ V (whichever is greater)}, V_{BIAS} = OPEN, V_{OUT(NOM)} = 0.8 \text{ V}, V_{EN} = 1.1 \text{ V}, C_{OUT} = 47 \text{ uF } // 10 \text{ µF} // 10 \text{ µF}, C_{NR/SS} = 10 \text{ nF}, C_{FF} = 10 \text{ nF}, \text{ and PG pin pulled up to } V_{IN} \text{ with } 100 \text{ k}\Omega \text{ (unless otherwise noted)}.$

$T_{A} = 25^{\circ}C, V_{IN} = 1.4 \text{ V or } V_{IN} = V_{OUT(NOM)} + 0.4 \text{ V (whichever is greater), } V_{BIAS} = OPEN,$  $V_{OUT(NOM)} = 0.8 \text{ V, } V_{EN} = 1.1 \text{ V, } C_{OUT} = 47 \text{ uF } / / 10 \text{ µF/} 10 \text{ µF, } C_{NR/SS} = 10 \text{ nF, } C_{FF} = 10 \text{ nF, and}$ PG pin pulled up to V<sub>IN</sub> with 100 kΩ (unless otherwise noted).

$T_{A} = 25^{\circ}C, V_{IN} = 1.4 \text{ V or } V_{IN} = V_{OUT(NOM)} + 0.4 \text{ V (whichever is greater), } V_{BIAS} = OPEN,$  $V_{OUT(NOM)} = 0.8 \text{ V}, V_{EN} = 1.1 \text{ V}, C_{OUT} = 47 \text{ uF } // 10 \text{ µF/} 10 \text{ µF, } C_{NR/SS} = 10 \text{ nF, } C_{FF} = 10 \text{ nF, and}$ PG pin pulled up to V<sub>IN</sub> with 100 kΩ (unless otherwise noted).

7

## **Typical application circuit**

### Figure 7-1 Typical GD30LD1003x application circuit with adjustable resistance

#### Table 7-1 Adjusted VOUT by external feedback resistor

| N 00            | External Feed | back Resistor |

|-----------------|---------------|---------------|

| Vout <b>(V)</b> | R1 (kΩ)       | R2(kΩ)        |

| 0.80            | 0             | NC            |

| 0.90            | 12.1          | 97.6          |

| 1.00            | 12.1          | 48.7          |

| 1.10            | 12.1          | 32.4          |

| 1.20            | 12.1          | 24.3          |

| 1.50            | 12.1          | 13.7          |

| 1.80            | 12.1          | 9.76          |

| 1.90            | 12.1          | 8.87          |

| 2.50            | 12.1          | 5.76          |

| 2.85            | 12.1          | 4.75          |

| 3.00            | 12.1          | 4.42          |

| 3.30            | 12.1          | 3.83          |

| 3.60            | 12.1          | 3.48          |

| 4.50            | 12.1          | 2.61          |

| 5.00            | 12.1          | 2.32          |

| 5.20            | 12.1          | 2.2           |

1.8V Fixed VOUT (VOUT = VFB + 200mV + 800mV = 1.8V)

| V <sub>FB</sub> = 0.8 V, SNS connect to V <sub>OUT</sub> |      |       |       |       |       |      |  |  |  |

|----------------------------------------------------------|------|-------|-------|-------|-------|------|--|--|--|

| <b>V</b> оит <b>(V)</b>                                  | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |  |  |  |

| 0.80                                                     | OPEN | OPEN  | OPEN  | OPEN  | OPEN  | OPEN |  |  |  |

| 0.85                                                     | GND  | OPEN  | OPEN  | OPEN  | OPEN  | OPEN |  |  |  |

| 0.90                                                     | OPEN | GND   | OPEN  | OPEN  | OPEN  | OPEN |  |  |  |

| 0.95                                                     | GND  | GND   | OPEN  | OPEN  | OPEN  | OPEN |  |  |  |

| 1.00                                                     | OPEN | OPEN  | GND   | OPEN  | OPEN  | OPEN |  |  |  |

| 1.05                                                     | GND  | OPEN  | GND   | OPEN  | OPEN  | OPEN |  |  |  |

| 1.10                                                     | OPEN | GND   | GND   | OPEN  | OPEN  | OPEN |  |  |  |

| 1.15                                                     | GND  | GND   | GND   | OPEN  | OPEN  | OPEN |  |  |  |

| 1.20                                                     | OPEN | OPEN  | OPEN  | GND   | OPEN  | OPEN |  |  |  |

| 1.25                                                     | GND  | OPEN  | OPEN  | GND   | OPEN  | OPEN |  |  |  |

| 1.30                                                     | OPEN | GND   | OPEN  | GND   | OPEN  | OPEN |  |  |  |

| 1.35                                                     | GND  | GND   | OPEN  | GND   | OPEN  | OPEN |  |  |  |

| 1.40                                                     | OPEN | OPEN  | GND   | GND   | OPEN  | OPEN |  |  |  |

| 1.45                                                     | GND  | OPEN  | GND   | GND   | OPEN  | OPEN |  |  |  |

| 1.50                                                     | OPEN | GND   | GND   | GND   | OPEN  | OPEN |  |  |  |

| 1.55                                                     | GND  | GND   | GND   | GND   | OPEN  | OPEN |  |  |  |

| 1.60                                                     | OPEN | OPEN  | OPEN  | OPEN  | GND   | OPEN |  |  |  |

| 1.65                                                     | GND  | OPEN  | OPEN  | OPEN  | GND   | OPEN |  |  |  |

| 1.70                                                     | OPEN | GND   | OPEN  | OPEN  | GND   | OPEN |  |  |  |

| 1.75                                                     | GND  | GND   | OPEN  | OPEN  | GND   | OPEN |  |  |  |

| 1.80                                                     | OPEN | OPEN  | GND   | OPEN  | GND   | OPEN |  |  |  |

| 1.85                                                     | GND  | OPEN  | GND   | OPEN  | GND   | OPEN |  |  |  |

| 1.90                                                     | OPEN | GND   | GND   | OPEN  | GND   | OPEN |  |  |  |

| 1.95                                                     | GND  | GND   | GND   | OPEN  | GND   | OPEN |  |  |  |

| 2.00                                                     | OPEN | OPEN  | OPEN  | GND   | GND   | OPEN |  |  |  |

Table 7-2 Adjusted VOUT by pin-setting

| V <sub>FB</sub> = 0.8 V, SNS connect to V <sub>OUT</sub> |      |       |       |       |       |      |  |  |

|----------------------------------------------------------|------|-------|-------|-------|-------|------|--|--|

| <b>V</b> оυт <b>(V)</b>                                  | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |  |  |

| 2.05                                                     | GND  | OPEN  | OPEN  | GND   | GND   | OPEN |  |  |

| 2.10                                                     | OPEN | GND   | OPEN  | GND   | GND   | OPEN |  |  |

| 2.15                                                     | GND  | GND   | OPEN  | GND   | GND   | OPEN |  |  |

| 2.20                                                     | OPEN | OPEN  | GND   | GND   | GND   | OPEN |  |  |

| 2.25                                                     | GND  | OPEN  | GND   | GND   | GND   | OPEN |  |  |

| 2.30                                                     | OPEN | GND   | GND   | GND   | GND   | OPEN |  |  |

| 2.35                                                     | GND  | GND   | GND   | GND   | GND   | OPEN |  |  |

| 2.40                                                     | OPEN | OPEN  | OPEN  | OPEN  | OPEN  | GND  |  |  |

| 2.45                                                     | GND  | OPEN  | OPEN  | OPEN  | OPEN  | GND  |  |  |

| 2.50                                                     | OPEN | GND   | OPEN  | OPEN  | OPEN  | GND  |  |  |

| 2.55                                                     | GND  | GND   | OPEN  | OPEN  | OPEN  | GND  |  |  |

| 2.60                                                     | OPEN | OPEN  | GND   | OPEN  | OPEN  | GND  |  |  |

| 2.65                                                     | GND  | OPEN  | GND   | OPEN  | OPEN  | GND  |  |  |

| 2.70                                                     | OPEN | GND   | GND   | OPEN  | OPEN  | GND  |  |  |

| 2.75                                                     | GND  | GND   | GND   | OPEN  | OPEN  | GND  |  |  |

| 2.80                                                     | OPEN | OPEN  | OPEN  | GND   | OPEN  | GND  |  |  |

| 2.85                                                     | GND  | OPEN  | OPEN  | GND   | OPEN  | GND  |  |  |

| 2.90                                                     | OPEN | GND   | OPEN  | GND   | OPEN  | GND  |  |  |

| 2.95                                                     | GND  | GND   | OPEN  | GND   | OPEN  | GND  |  |  |

| 3.00                                                     | OPEN | OPEN  | GND   | GND   | OPEN  | GND  |  |  |

| 3.05                                                     | GND  | OPEN  | GND   | GND   | OPEN  | GND  |  |  |

| 3.10                                                     | OPEN | GND   | GND   | GND   | OPEN  | GND  |  |  |

| 3.15                                                     | GND  | GND   | GND   | GND   | OPEN  | GND  |  |  |

| 3.20                                                     | OPEN | OPEN  | OPEN  | OPEN  | GND   | GND  |  |  |

| 3.25                                                     | GND  | OPEN  | OPEN  | OPEN  | GND   | GND  |  |  |

| 3.30                                                     | OPEN | GND   | OPEN  | OPEN  | GND   | GND  |  |  |

| 3.35                                                     | GND  | GND   | OPEN  | OPEN  | GND   | GND  |  |  |

| 3.40                                                     | OPEN | OPEN  | GND   | OPEN  | GND   | GND  |  |  |

| 3.45                                                     | GND  | OPEN  | GND   | OPEN  | GND   | GND  |  |  |

| 3.50                                                     | OPEN | GND   | GND   | OPEN  | GND   | GND  |  |  |

| 3.55                                                     | GND  | GND   | GND   | OPEN  | GND   | GND  |  |  |

| 3.60                                                     | OPEN | OPEN  | OPEN  | GND   | GND   | GND  |  |  |

| 3.65                                                     | GND  | OPEN  | OPEN  | GND   | GND   | GND  |  |  |

| 3.70                                                     | OPEN | GND   | OPEN  | GND   | GND   | GND  |  |  |

| 3.75                                                     | GND  | GND   | OPEN  | GND   | GND   | GND  |  |  |

| 3.80                                                     | OPEN | OPEN  | GND   | GND   | GND   | GND  |  |  |

| 3.85                                                     | GND  | OPEN  | GND   | GND   | GND   | GND  |  |  |

| 3.90                                                     | OPEN | GND   | GND   | GND   | GND   | GND  |  |  |

| 3.95                                                     | GND  | GND   | GND   | GND   | GND   | GND  |  |  |

## 8 Layout guideline

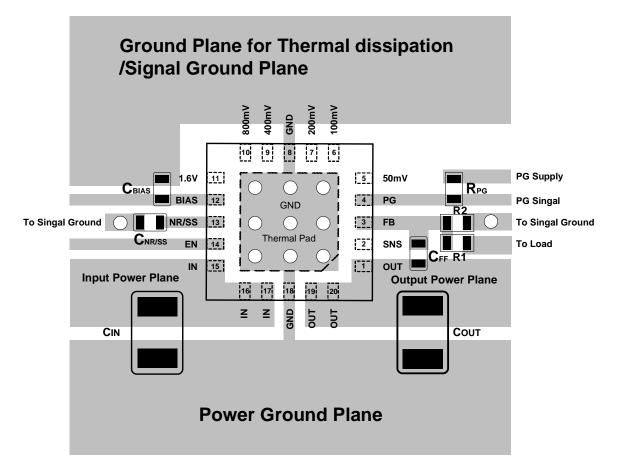

Figure 8-1 Typical GD30LD1003x layout guideline

#### Notes:

- 1. The capacitor  $C_{IN}$  and  $C_{OUT}$  should be placed on the top layer to reduce parasitic parameters.

- 2. All capacitors are as close as possible to the corresponding pins of the LDO.

## 9 Package information

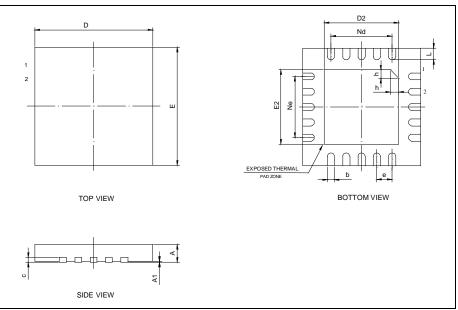

## 9.1 QFN20 package outline dimensions

#### Figure 9-1 QFN20 package outline

#### Table 9-1 QFN20 dimensions

| Symbol | Min  | Тур     | Мах  |

|--------|------|---------|------|

| A      | 0.70 | 0.75    | 0.80 |

| A1     | —    | 0.02    | 0.05 |

| b      | 0.25 | 0.30    | 0.35 |

| С      | 0.18 | 0.20    | 0.25 |

| D      | 4.90 | 5.00    | 5.10 |

| D2     | 3.05 | 3.15    | 3.25 |

| E      | 4.90 | 5.00    | 5.10 |

| E2     | 3.05 | 3.15    | 3.25 |

| е      |      | 0.65BSC |      |

| h      | 0.30 | 0.35    | 0.40 |

| L      | 0.45 | 0.55    | 0.65 |

| Nd     |      | 2.60BSC |      |

| Ne     |      | 2.60BSC |      |

(Original dimensions are in millimeters)

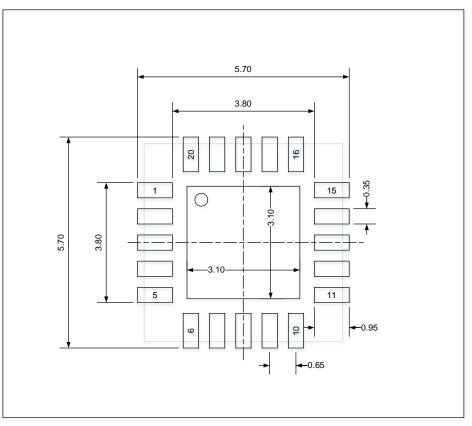

#### Figure 9-2 QFN20 recommend footprint

(All dimensions are in millimeters)

### 9.2 Thermal characteristics

Thermal resistance is used to characterize the thermal performance of the package device, which is represented by the Greek letter " $\Theta$ ". For semiconductor devices, thermal resistance represents the steady-state temperature rise of the chip junction due to the heat dissipated on the chip surface.

$\Theta_{JA}$ : Thermal resistance, junction-to-ambient.

$\Theta_{JB}$ : Thermal resistance, junction-to-board.

$\Theta_{JC}$ : Thermal resistance, junction-to-case.

$\Psi_{\text{JB}}$ : Thermal characterization parameter, junction-to-board.

$\Psi_{\text{JT}}$ : Thermal characterization parameter, junction-to-top center.

$\Theta_{JA} = (T_J - T_A)/P_D$

$\Theta_{\rm JB} = (T_{\rm J} - T_{\rm B})/P_{\rm D}$

$\Theta_{\text{JC}} = (T_{\text{J}} - T_{\text{C}})/P_{\text{D}}$

Where,  $T_J$  = Junction temperature.

T<sub>A</sub> = Ambient temperature

T<sub>B</sub> = Board temperature

$T_{C}$  = Case temperature which is monitoring on package surface

P<sub>D</sub> = Total power dissipation

$\Theta_{JA}$  represents the resistance of the heat flows from the heating junction to ambient air. It is an indicator of package heat dissipation capability. Lower  $\Theta_{JA}$  can be considerate as better overall thermal performance.  $\Theta_{JA}$  is generally used to estimate junction temperature.

$\Theta_{\mbox{\scriptsize JB}}$  is used to measure the heat flow resistance between the chip surface and the PCB board.