# Low-Voltage H-Bridge Driver

# 1 Features

- H-Bridge Motor Driver

- Drive a DC Motor or Other Load

- Low MOSFET ON-Resistance:

HS + LS 850mΩ

- 1 A Maximum Drive Current

- Separate Motor and Logic-Supply Pins:

0 V to 10 V Motor Operating Supply Voltage

- 1.6 V to 7 V Logic Supply Voltage

- Separate Logic and Motor Power Supply Pins

- Standard PWM Interface (IN1/IN2)

- Low Power Sleep Mode, Maximum Sleep Current 120 nA

– nSLEEP pin

- Small Package and Footprint

- 8 pin DFN (With Thermal Pad)

- 2.00mm x 2.00mm

- Protection Features

- VCC Undervoltage Lockout (UVLO)

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

# 2 Applications

- Battery-Powered:

- Cameras

- DSLR Lenses

- Consumer Products

- Toys

- Robotics

- Medical Devices

# 3 Description

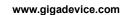

The GD30DR3801 provides an integrated motor driver solution for cameras, consumer products, toys, and other low voltage or battery-powered motion control applications. The device has an H-bridge driver, and drives one DC motors, as well as other devices like solenoids. The output driver block consists of N-channel power MOSFETs configured as an H-bridge to drive the motor winding. An internal charge pump generates gate drive voltages.

The GD30DR3801 supplies up to 1A of output current. The operates on a motor power supply voltage from 0V to 10 V, and control logic can operate on 1.6 V to 7 V rails.

The GD30DR3801 device has a PWM(IN/IN) input interface. Internal shutdown functions are provided for overcurrent protection, short circuit protection, undervoltage lockout protection, and overtemperature protection.

## **Device Information<sup>1</sup>**

| ORDERING CODE    | PACKAGE | BODY SIZE (NOM)   |

|------------------|---------|-------------------|

| GD30DR3801WETR-K | DFN (8) | 2.00 mm × 2.00 mm |

1. For packaging details, see *Package Information* section.

**Simplified Application Schematic**

# **Table of Contents**

| 1   | Featu   | Ires                             | 1  |

|-----|---------|----------------------------------|----|

| 2   | Appli   | cations                          | 1  |

| 3   | Desc    | ription                          | 1  |

| Tab | le of C | Contents                         | 2  |

| 4   | Devi    | ce Overview                      | 3  |

|     | 4.1     | Pinout and Pin Assignment        | 3  |

|     | 4.2     | Pin Description                  | 3  |

| 5   | Para    | neter Information                | 4  |

|     | 5.1     | Absolute Maximum Ratings         | 4  |

|     | 5.2     | Recommended Operation Conditions | 4  |

|     | 5.3     | Electrical Sensitivity           | 4  |

|     | 5.4     | Electrical Characteristics       | 5  |

|     | 5.5     | Timing Requirements              | 6  |

| 6   | Func    | tional Description               | 7  |

|     | 6.1     | Block Diagram                    | 7  |

|     | 6.2     | Operation                        | 7  |

|     | 6.3     | Device Modes Description         | 9  |

| 7   | Appli   | cation Information               | 10 |

|     | 7.1     | Typical Application Circuit      | 10 |

|     | 7.2     | Design Example                   | 10 |

|     | 7.3     | Detailed Design Description      | 10 |

|     | 7.4     | Power Dissipation                | 10 |

|     | 7.5     | Typical Application Curves       |    |

| 8   | Layo    | ut Guidelines and Example        | 13 |

|     | 8.1     | Layout Guidelines                |    |

|     | 8.2     | Layout Example                   | 13 |

| 9   | Pack    | age Information                  | 14 |

|     | 9.1     | Outline Dimensions               |    |

|     | 9.2     | Recommended Land Pattern         | 16 |

| 10  | Orde    | ring Information                 | 17 |

|     |         |                                  |    |

# 4 Device Overview

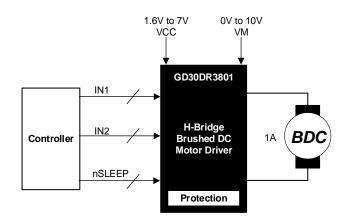

## 4.1 Pinout and Pin Assignment

# 4.2 Pin Description

| P           | N           |   | FUNCTION                                                               |

|-------------|-------------|---|------------------------------------------------------------------------|

| NAME        | DFN8        |   | FUNCTION                                                               |

| VM          | 1           | Р | Power supply. Connect a 0.1uF bypass capacitor to ground, as well as   |

| VIVI        | Ι           | I | sufficient bulk capacitance, rated for the VM voltage.                 |

| OUT1        | 2           | 0 | Bridge output 1. Connect to DC motor winding.                          |

| OUT2        | 3           | 0 | Bridge output 2. Connect to DC motor winding.                          |

| GND         | 4           | Р | Device ground. Connect to board ground.                                |

| IN2         | 5           | ļ | Bridge input 2. Logic high sets OUT2 high. Internal pulldown resistor. |

| IN1         | 6           | ļ | Bridge input 1. Logic high sets OUT1 high. Internal pulldown resistor. |

|             |             |   | Sleep mode input. Logic low: the device enters low-power sleep mode.   |

| nSLEEP      | 7           | I | Logic high: the device operates normal mode. Internal pulldown         |

|             |             |   | resistor                                                               |

| VCC         | 8           | Р | Device supply. Connect a 0.1uF bypass capacitor to ground, rated for   |

| VCC         | 0           | F | the VCC voltage.                                                       |

|             |             |   | Power ground, connect to board ground, use large ground plane for      |

| Thermal pad | Thermal pad | Р | good thermal dissipation, and multiple nearby vias connecting those    |

|             |             |   | planes.(See <i>Layout Example</i> ).                                   |

1. I = input, O = output, P = power, G = ground.

# 5 Parameter Information

## 5.1 Absolute Maximum Ratings

Exceeding the operating temperature range (unless otherwise noted)<sup>1,2</sup>

| SYMBOL           | PARAMETER                       | MIN                | MAX | UNIT |

|------------------|---------------------------------|--------------------|-----|------|

| VM               | Motor power supply voltage      | -0.3               | 11  | V    |

| VCC              | Logic power supply voltage      | -0.3               | 7   | V    |

| INx, nSLEEP      | Control input pin voltage       | -0.5               | Vcc | V    |

| OUTx             | Peak motor drive output current | Internally limited |     | Α    |

| TJ               | Operating junction temperature  | -40                | 150 | °C   |

| T <sub>stg</sub> | Storage temperature             | -60                | 150 | °C   |

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. All voltage values are with respect to network ground terminal.

## 5.2 Recommended Operation Conditions

| SYMBOL <sup>1,2</sup> | PARAMETER                             | MIN | ТҮР | MAX | UNIT |

|-----------------------|---------------------------------------|-----|-----|-----|------|

| VM                    | Motor power supply voltage            | 0   |     | 10  | V    |

| VCC                   | Logic power supply voltage            | 1.6 |     | 7.0 | V    |

| VLOGIC                | Logic level input voltage             | 0   |     | VCC | V    |

| lout                  | Continuous motor drive output current | 0   |     | 1.0 | А    |

| f <sub>pwm</sub>      | Externally applied PWM frequency      | 0   |     | 250 | kHz  |

| T <sub>A</sub>        | Operating ambient temperature         | -40 |     | 85  | °C   |

1. The device is not guaranteed to function outside of its operating conditions.

2. Application Information section for further information.

# 5.3 Electrical Sensitivity

| SYMBOL                | CONDITIONS                                                          | VALUE | UNIT |

|-----------------------|---------------------------------------------------------------------|-------|------|

| V <sub>ESD(HBM)</sub> | Human-body model (HBM), ANSI/ESDA/JEDEC JS-001-2017 <sup>1</sup>    | ±4000 | V    |

| VESD(CDM)             | Charge-device model (CDM), ANSI/ESDA/JEDEC JS-002-2022 <sup>2</sup> | ±2000 | V    |

1. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

2. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.4 Electrical Characteristics

### $T_A = 25^{\circ}C$ (unless otherwise noted).

| SYMBOL              | PARAMETER                         | CONDITIONS                                  | MIN                 | TYP  | MAX                  | UNIT |

|---------------------|-----------------------------------|---------------------------------------------|---------------------|------|----------------------|------|

| POWER SU            | PPLY(VM, VCC)                     |                                             |                     |      |                      |      |

| VM                  | VM operating voltage              |                                             | 0                   |      | 10                   | V    |

|                     |                                   | No PWM, no load                             |                     | 40   | 100                  | μA   |

| I <sub>VM</sub>     | VM operating supply current       | 50 kHz PWM, no load                         |                     | 0.15 | 1.0                  | mA   |

| I <sub>VMQ</sub>    | VM sleep mode supply current      | nSLEEP = 0                                  |                     | 30   | 95                   | nA   |

|                     | VCC encreting cumply current      | No PWM, no load                             |                     | 100  | 200                  | μA   |

| lvcc                | VCC operating supply current      | 50 kHz PWM, no load                         |                     | 0.18 | 1.0                  | mA   |

| lvccq               | VCC sleep mode supply current     | nSLEEP = 0                                  |                     | 5    | 25                   | nA   |

| N/                  |                                   | VCC rising                                  |                     |      | 1.6                  | V    |

| Vuvlo               | VCC undervoltage lockout voltage  | VCC falling                                 |                     |      | 1.5                  | V    |

| LOGIC-LEV           | EL INPUTS(IN1, IN2, nSLEEP)       | ·                                           |                     |      |                      | -    |

| VIL                 | Input low voltage                 |                                             |                     |      | $0.25 \times V_{CC}$ | V    |

| VIH                 | Input high voltage                |                                             | 0.5×V <sub>CC</sub> |      |                      | V    |

| IIL                 | Input low current                 | V <sub>IN</sub> = 0                         | -5                  |      | 5                    | μA   |

| Іін                 | Input high current                | V <sub>IN</sub> = 3.3V                      |                     |      | 50                   | μA   |

| Rpd                 | Pulldown resistance               |                                             |                     | 100  |                      | KΩ   |

| H-BRIDGE            | FETS(OUT1, OUT2)                  |                                             |                     |      |                      | _    |

| R <sub>DS(ON)</sub> | HS+LS FET on resistance           | VM = 5V, VCC = 3V,<br>Io = 800mA, TJ = 25°C |                     | 850  |                      | mΩ   |

| IOFF                | OFF-state leakage current         | V <sub>OUTx</sub> = 0V                      | -200                |      | 200                  | nA   |

| PROTECTIO           |                                   | 1                                           | I                   |      |                      |      |

| I <sub>OFF</sub>    | Overcurrent protection trip level |                                             | 1.2                 |      |                      | Α    |

| tdeg                | Overcurrent de-glitch time        |                                             |                     | 1    |                      | μs   |

| tocr                | Overcurrent protection retry time |                                             |                     | 1    |                      | ms   |

| t <sub>TSD</sub> 1  | Thermal shutdown temperature      | Die temperature                             | 150                 | 160  | 190                  | °C   |

|                     |                                   |                                             |                     |      |                      |      |

1. Not tested in production; based on design and characterization data.

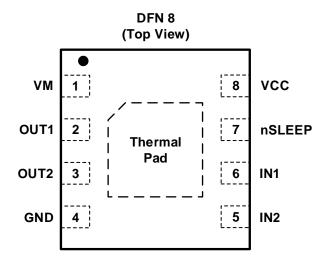

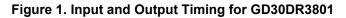

# 5.5 Timing Requirements

### VM = 5V, VCC = 3V, $R_L$ = 20 $\Omega$ , $T_A$ = 25°C.

| SYMBOL            | PARAMETER                                      | MIN | MAX | UNIT |

|-------------------|------------------------------------------------|-----|-----|------|

| t1                | Output enable time                             |     | 300 | ns   |

| t2                | Output disable time                            |     | 300 | ns   |

| t <sub>3</sub>    | Delay time, INx high to OUTx high              |     | 160 | ns   |

| t4                | t <sub>4</sub> Delay time, INx low to OUTx low |     | 160 | ns   |

| t5                | t <sub>5</sub> Output rise time                |     | 188 | ns   |

| t <sub>6</sub>    | t <sub>6</sub> Output fall time                |     | 188 | ns   |

| t <sub>wake</sub> | Wake time, nSLEEP rising edge to part active   |     | 30  | μs   |

# 6 Functional Description

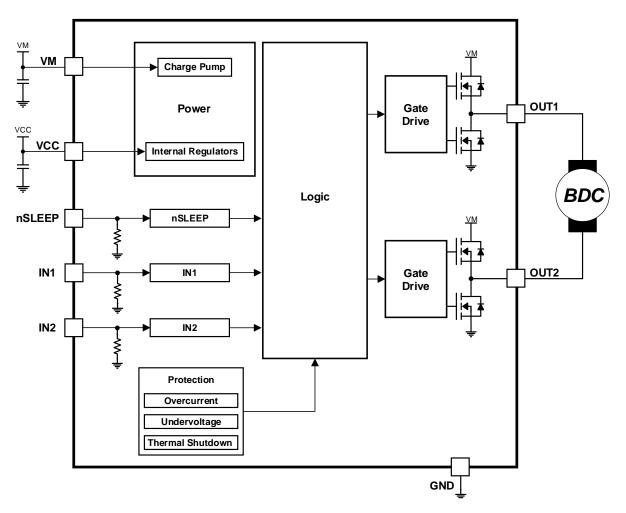

## 6.1 Block Diagram

Figure 2. GD30DR3801 Functional Block Diagram

# 6.2 Operation

The GD30DR3801 serves as an H-bridge driver capable of powering a single DC motor or other devices, such as solenoids. It regulates its outputs through a PWM interface (IN1/IN2) and incorporates a low-power sleep mode, which can be activated via the nSLEEP pin. This device significantly simplifies motor driver systems by integrating the necessary driver FETs and FET control circuitry into a single unit, thus reducing component count. Furthermore, the GD30DR3801 device includes advanced protection features, going beyond traditional discrete implementations, which encompass undervoltage lockout, overcurrent protection, and thermal shutdown.

# 6.2.1 Bridge Control

The GD30DR3801 utilizes a PWM input interface, which is alternatively referred to as an IN/IN interface. Each input pin corresponds to the control of an individual output.

Table 1 shows the logic for the GD30DR3801 device.

| nSLEEP | IN1 | IN2 | OUT1 | OUT2 | FUNCTION (DC MOTOR) |

|--------|-----|-----|------|------|---------------------|

| 0      | Х   | Х   | Z    | Z    | Coast               |

| 1      | 0   | 0   | Z    | Z    | Coast               |

| 1      | 0   | 1   | L    | Н    | Reverse             |

| 1      | 1   | 0   | Н    | L    | Forward             |

| 1      | 1   | 1   | L    | L    | Brake               |

Table 1. H-Bridge Control

## 6.2.2 Sleep Mode

The GD30DR3801 enters a low-power sleep mode when the nSLEEP pin is set to a logic-low state. In this mode, all internal circuitry is powered down.

### 6.2.3 Power Supplies and Input Pins

The input pins can be driven within the recommended operating conditions with or without the presence of VCC, VM or with both power supplies connected. There is no current leakage path to the power supply. Each input pin includes a weak pulldown resistor (approximately 100 k $\Omega$ ) connected to the ground.

The VCC and VM supplies can be applied and removed in any order. When the VCC supply is disconnected, the device transitions into a low-power state and expends minimal current from the VM supply. The VCC and VM pins can be connected if the supply voltage is in the range of 1.6V to 7.0V.

The VM voltage supply lacks undervoltage-lockout protection (UVLO). As long as VCC is above 1.6V, the internal device logic remains active. This implies that the VM pin voltage can drop to 0V. However, it's important to note that the load may not be adequately powered at low VM voltages.

### 6.2.4 Protection Circuits

The GD30DR3801 is equipped with comprehensive protections against VCC undervoltage, overcurrent and overtemperature incidents.

### 6.2.4.1 VCC undervoltage lockout(UVLO)

If the voltage on the VCC pin drops below the undervoltage lockout threshold at any point, all FETs in the H-bridge are disabled. Normal operation resumes when the voltage on the VCC pin rises above the UVLO threshold.

#### 6.2.4.2 Overcurrent protection (OCP)

Each FET is equipped with an analog current-limit circuit that controls the current by cutting off the gate drive. If this analog current limit persists for a duration exceeding  $t_{DEG}$ , all FETs in the H-bridge are disabled. Normal operation automatically resumes after  $t_{RETRY}$  has passed. Overcurrent conditions are detected in both the high-side and low-side devices. An overcurrent condition is triggered by a short circuit between the VM pin and GND or between the OUT1 pin and the OUT2 pin.

#### 6.2.4.3 Thermal shutdown (TSD)

If the temperature of the integrated circuit surpasses safe thresholds, all FETs within the H-bridge are disabled. Operation automatically resumes once the temperature returns into a safe range.

| FAULT                  | CONDITION                     | H-BRIDGE | INTERNAL CIRCUIT | RECOVERY               |

|------------------------|-------------------------------|----------|------------------|------------------------|

| VCC undervoltage(UVLO) | V <sub>CC</sub> < 1.5V        | Disabled | Disabled         | V <sub>CC</sub> > 1.6V |

| Overcurrent(OCP)       | I <sub>OUT</sub> > 1.2A (MIN) | Disabled | Operating        | tocr                   |

| Thermal Shutdown(TSD)  | T <sub>J</sub> > 150°C (MIN)  | Disabled | Operating        | T <sub>J</sub> < 150°C |

#### **Table 2. Fault Conditions Summary**

### 6.3 Device Modes Description

The GD30DR3801 remains operational unless the nSLEEP pin is set to a logic low state. When in sleep mode, the H-bridge FETs are deactivated and set to a high-impedance state (Hi-Z). The GD30DR3801 device is automatically awakened from sleep mode when the nSLEEP pin is set to a logic high state.

The H-bridge outputs are disabled when undervoltage lockout, overcurrent or overtemperature faults occur.

| OPERATING MODE    | CONDITION               | H-BRIDGE  | INTERNAL CIRCUIT |

|-------------------|-------------------------|-----------|------------------|

| Operating         | nSLEEP high             | Operating | Operating        |

| Sleep mode        | nSLEEP low              | Disabled  | Disabled         |

| Fault encountered | Any fault condition met | Disabled  | See Table 2      |

#### Table 3. Mode of Operation

# 7 Application Information

The GD30DR3801 is typically used to drive one brushed DC motor or other devices like solenoids.

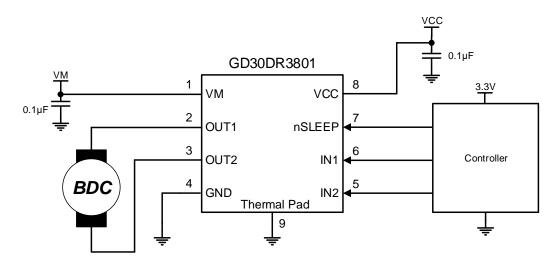

# 7.1 Typical Application Circuit

Figure 3. Schematic of GD30DR3801 Application

## 7.2 Design Example

For this design example, use the parameters in Table 4.

#### **Table 4. Design Parameters**

| PARAMETER            | EXAMPLE VALUE |

|----------------------|---------------|

| Motor Supply Voltage | 5V            |

| Logic Supply Voltage | 3.3V          |

| Target RMS Current   | 0.5A          |

## 7.3 Detailed Design Description

## 7.3.1 Motor Voltage

The motor voltage to use will depend on the ratings of the motor selected and the desired RPM. A higher voltage spins a brushed DC motor faster with the same PWM duty cycle applied to the power FETs. A higher voltage also increases the rate of current change through the inductive motor windings.

## 7.3.2 Low Power Mode

When entering sleep mode, GD recommends keeping all input pins low level to minimize system power consumption.

# 7.4 Power Dissipation

Power dissipation in the GD30DR3801 is dominated by the power dissipated in the output FET resistance, or R<sub>DS(on)</sub>. There is additional power due to PWM switching losses, which are dependent on PWM frequency, rise

and fall time, and VM supply voltages. These switching losses are typically on the order of 10% to 30% of DC power dissipation.

The power dissipation of the GD30DR3801 device is on function of RMS motor current and FET ON-resistance of each output.

$$P_{D} \approx I_{RMS}^{2} \times \left( R_{HS_{DS}(ON)} + R_{LS_{DS}(ON)} \right)$$

(1)

where

- P<sub>D</sub> is the device power dissipation

- R<sub>HS\_DS(ON)</sub> is the resistance of the high-side FET

- RLS\_DS(ON) is the resistance of the low-side FET

- · IRMS is the RMS or DC output current being supplied to the load

$R_{DS(ON)}$  increases with temperature, so as the device heats, the power dissipation increases. This must be taken into consideration when sizing the heatsink.

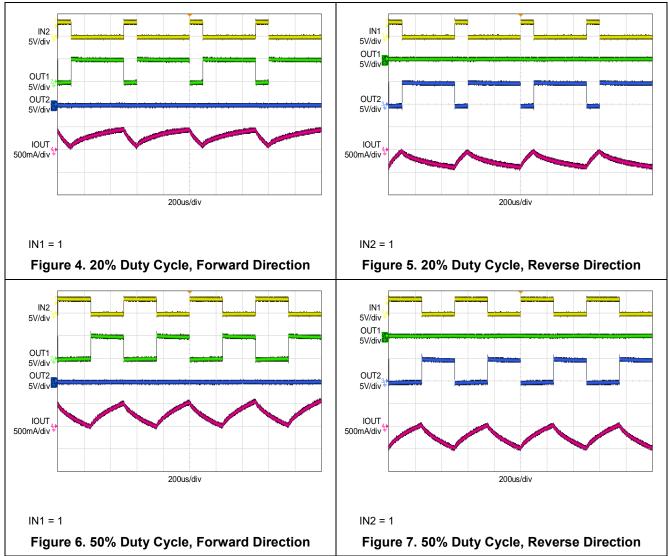

## 7.5 Typical Application Curves

# 8 Layout Guidelines and Example

### 8.1 Layout Guidelines

Low ESR ceramic capacitors should be utilized for the VM and VCC to GND bypass capacitors. 0.1uF X5R or X7R types are recommended. These capacitors should be placed as close to the VM and VCC pins as possible with a thick trace or ground plane connection to the device GND pin.

In addition, bulk capacitor is required on the VM pin. This bulk capacitor can be ceramic or electrolytic type, but should also be placed as close as possible to the VM pin to minimize the loop inductance.

The high-current device outputs should use wide metal trace, and numerous vias should be used when connecting PCB layers.

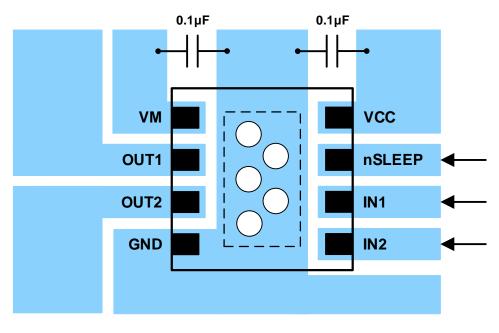

## 8.2 Layout Example

Recommended layout and placement is shown in the following diagram.

Figure 8. Simplified Layout Example

# 9 Package Information

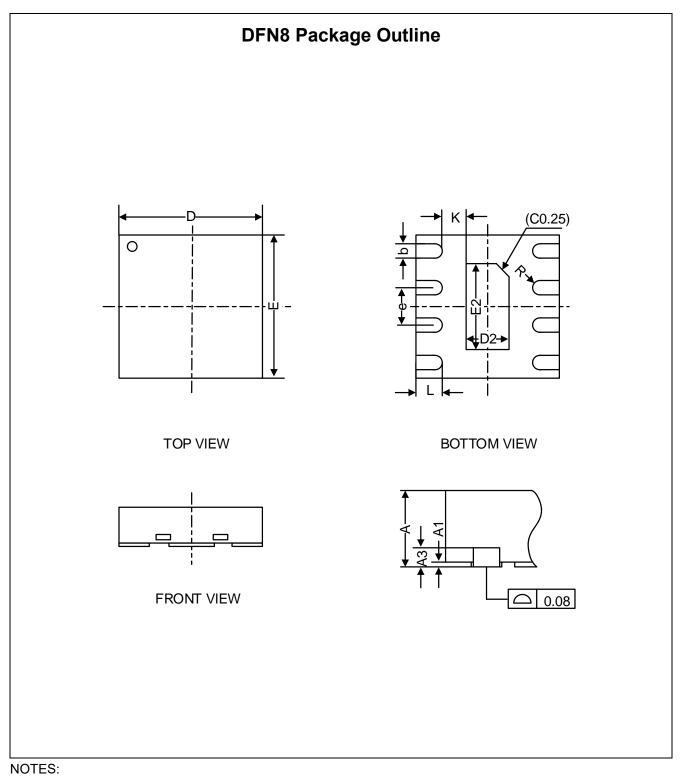

### 9.1 Outline Dimensions

- 1. All dimensions are in millimeters.

- 2. Package dimensions does not include mold flash, protrusions, or gate burrs.

- 3. Refer to the Table 5 *DFN8 dimensions(mm)*.

### Table 5. DFN8 dimensions(mm)

| SYMBOL | MIN     | ТҮР  | MAX  |  |  |  |

|--------|---------|------|------|--|--|--|

| А      | 0.70    | 0.75 | 0.80 |  |  |  |

| A1     | 0       | 0.02 | 0.05 |  |  |  |

| A3     | 0.20REF |      |      |  |  |  |

| b      | 0.15    | 0.20 | 0.25 |  |  |  |

| D      | 1.90    | 2.00 | 2.10 |  |  |  |

| E      | 1.90    | 2.00 | 2.10 |  |  |  |

| D2     | 0.50    | 0.60 | 0.70 |  |  |  |

| E2     | 1.10    | 1.20 | 1.30 |  |  |  |

| e      | 0.40    | 0.50 | 0.60 |  |  |  |

| К      | 0.20    |      |      |  |  |  |

| L      | 0.30    | 0.35 | 0.40 |  |  |  |

| R      | 0.09    |      |      |  |  |  |

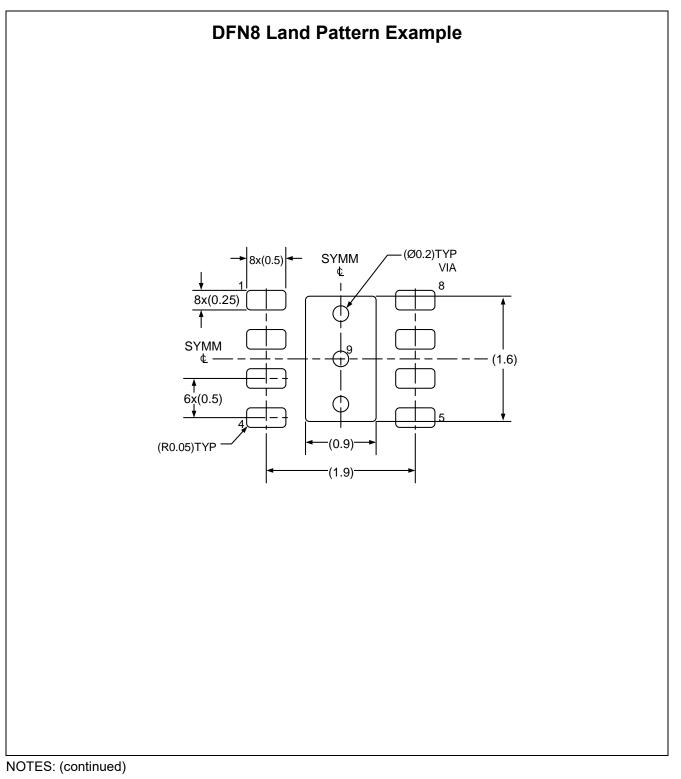

### 9.2 Recommended Land Pattern

- 1. Refer to the IPC-7351 can also help you complete the designs.

- 2. Exposed metal shown.

- 3. Drawing is 20X scale.

# **10 Ordering Information**

| Ordering Code    | Package Type | ECO Plan | Packing Type | MOQ  | OP Temp(°C)    |

|------------------|--------------|----------|--------------|------|----------------|

| GD30DR3801WETR-K | DFN8         | Green    | Tape & Reel  | 3000 | Industrial     |

|                  |              |          |              |      | -40°C to +85°C |

# **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company according to the laws of the People's Republic of China and other applicable laws. The Company reserves all rights under such laws and no Intellectual Property Rights are transferred (either wholly or partially) or licensed by the Company (either expressly or impliedly) herein. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no representations or warranties of any kind, express or implied, with regard to the merchantability and the fitness for a particular purpose of the Product, nor does the Company assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the sole responsibility of the user of this document to determine whether the Product is suitable and fit for its applications and products planned, and properly design, program, and test the functionality and safety of its applications and products planned using the Product. Unless otherwise expressly specified in the datasheet of the Product, the Product is designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only, and the Product is not designed or intended for use in (i) safety critical applications such as weapons systems, nuclear facilities, atomic energy controller, combustion controller, aeronautic or aerospace applications, traffic signal instruments, pollution control or hazardous substance management; (ii) life-support systems, other medical equipment or systems (including life support equipment and surgical implants); (iii) automotive applications or environments, including but not limited to applications for active and passive safety of automobiles (regardless of front market or aftermarket), for example, EPS, braking, ADAS (camera/fusion), EMS, TCU, BMS, BSG, TPMS, Airbag, Suspension, DMS, ICMS, Domain, ESC, DCDC, e-clutch, advancedlighting, etc.. Automobile herein means a vehicle propelled by a self-contained motor, engine or the like, such as, without limitation, cars, trucks, motorcycles, electric cars, and other transportation devices; and/or (iv) other uses where the failure of the device or the Product can reasonably be expected to result in personal injury, death, or severe property or environmental damage (collectively "Unintended Uses"). Customers shall take any and all actions to ensure the Product meets the applicable laws and regulations. The Company is not liable for, in whole or in part, and customers shall hereby release the Company as well as its suppliers and/or distributors from, any claim, damage, or other liability arising from or related to all Unintended Uses of the Product. Customers shall indemnify and hold the Company, and its officers, employees, subsidiaries, affiliates as well as its suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Product.

Information in this document is provided solely in connection with the Product. The Company reserves the right to make changes, corrections, modifications or improvements to this document and the Product described herein at any time without notice. The Company shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 GigaDevice - All rights reserved