# GigaDevice Semiconductor Inc.

# GD32H7xx Series Software Development Guide

# Application Notes AN111

Version 1.0

(May 2023)

# **Table of Contents**

| Table  | of Contents                                                          | 1  |

|--------|----------------------------------------------------------------------|----|

| List o | Figures                                                              | 3  |

| List o | Tables                                                               | 4  |

| 1. O   | /erview                                                              | 5  |

| 2. D   | velopment of software functions                                      | 6  |

| 2.1.   | Selection and configuration of Boot modes                            |    |

| 2.2.   | Instruction of PMU use-related issues                                | 7  |

| 2.2    |                                                                      |    |

| 2.2    | .2. POR_ON pin                                                       | 7  |

| 2.2    | .3. Programmer link issues in sleep mode                             | 8  |

|        | .4. Pxx pin and Pxx_C pin link issues in standby mode                |    |

| 2.2    | .5. Software configuration                                           | 8  |

| 2.3.   | Instruction of RCU use                                               | 8  |

| 2.4.   | Monitoring junction temperature                                      | 9  |

| 2.4    |                                                                      |    |

| 2.4    | 3, 1                                                                 |    |

|        | .3. JTM alarm function                                               |    |

| 2.4    | .4. Advices for high-temperature and high-speed conditions           | 10 |

| 2.5.   | Use of Secure JTAG                                                   | 10 |

| 2.6.   | Jlink debug issues                                                   | 13 |

| 2.7.   | Instruction of cache use                                             | 13 |

| 2.     | .1. Data consistency issues when using Dcache and DMA simultaneously | 13 |

| 2.     | .2. Use of cache and data alignment configuration                    | 14 |

| 2.8.   | Use of CAN filter                                                    | 15 |

| 2.9.   | Hardfault issue arising from non-aligned access to EXMC SDRAM        | 16 |

| 2.10   |                                                                      |    |

| 2.11   | •                                                                    |    |

| 2.12   | •                                                                    |    |

|        | · ·                                                                  |    |

| 2.13   |                                                                      |    |

| 2.14   |                                                                      |    |

|        | 4.1. SDIO clock configuration                                        |    |

|        | 4.2. SDIO power-on initialization                                    |    |

| ۷.     | T.O. DOS WIGHT COMMUNICATION                                         | ZJ |

| GigaDevice | GD32H7xx Series Software           | AN111<br>Development Guide |

|------------|------------------------------------|----------------------------|

| 2.14.4.    | Accessing eMMC Boot partition data | 26                         |

| 2.14.5.    | MDMA configuration                 | 26                         |

| 2.14.6.    | IDMA configuration                 | 28                         |

| 3. Revis   | ion history                        | 29                         |

# **List of Figures**

| Figure 2-1. Processes of power-on initialization and voltage switch of SD card | 22 |

|--------------------------------------------------------------------------------|----|

| Figure 2-2. Processes of power-on initialization and voltage switch of eMMC    | 23 |

| Figure 2-3. Tuning processes of SD card                                        | 25 |

| Figure 2-4. Flow chart of MDMA controlling the sending of CMD12                | 27 |

| Figure 2-5. Flow chart of MDMA controlling RAM data transfer                   | 27 |

# **List of Tables**

| Table 1-1. Applicable product                          | 5  |

|--------------------------------------------------------|----|

| Table 2-1. Selection of Boot mode                      |    |

| Table 2-2. API for cache operation                     | 14 |

| Table 2-3. ARMv7-M address mapping                     | 17 |

| Table 2-4. Configuring bus width of SD card            | 24 |

| Table 2-5. Configuring bus speed of SD card            | 24 |

| Table 2-6. Configuring bus mode of eMMC                | 24 |

| Table 2-7. Configuring bus speed of eMMC               | 24 |

| Table 2-8. Accessing partition commands and parameters | 26 |

| Table 3-1. Revision history                            | 29 |

### 1. Overview

This document is intended for GD32H7xx MCU, introducing how to build and debug GD32H7xx chip based projects and how to use each module. This application note aims to give an exemplary introduction to peripheral resources on GD32H7xx MCU so that users can know how to develop software rapidly with GD32H7xx chips.

Table 1-1. Applicable product

| Type | Model           |  |

|------|-----------------|--|

| MCU  | GD32H7xx Series |  |

## 2. Development of software functions

### 2.1. Selection and configuration of Boot modes

GD32H7xx provides different Boot modes whose difference mainly lies in booting location. In general, it includes secure Boot mode and standard Boot mode.

Secure Boot mode can only be initiated from ROM. For details, please refer to secure storage management of AN113 GD32H7xx series. After properly configuring option byte or SCR in Efuse and register in the secure area, users can initiate secure Boot mode. At the next start-up, SECURITY BOOT will be directly initiated regardless of other Boot-related configurations.

Standard Boot mode allows three Boot modes, including USER BOOT, SRAM BOOT, and SYSTEM BOOT. Boot mode can be selected through hardware BOOT pin together with Efuse and option bytes registers. When configuring, EFUSE is superior to option bytes. BOOT pin is adopted to select Boot address 0/1. When the BOOT pin level is low, the high bit of BOOT address is defined by BOOT\_ADDR0[15:0]. When the BOOT pin level is high, the high bit of BOOT address is defined by BOOT\_ADDR1[15:0]. High-level read protection configured in standard Boot mode is prohibited in some boot sectors. For details, please refer to the table below.

Table 2-1. Selection of Boot mode

| SCR | SPC[7:0]            | BOOT_ADDRESS (configured in BOOT_ADDRx (x = 0,1)) | BOOT mode               | Boot address |  |

|-----|---------------------|---------------------------------------------------|-------------------------|--------------|--|

| 1   | 1 x XXXX            |                                                   | SECURITY BOOT           | ROM          |  |

|     |                     | 0x9000_0000                                       | USER BOOT               | OSPI0        |  |

|     | High                | 0x7000_0000                                       | USER BOOT               | OSPI1        |  |

|     | protection<br>level | 0x0800_0000~max user<br>flash                     | USER BOOT               | BOOT_ADDRESS |  |

|     |                     | other                                             | USER BOOT               | 0x0800_0000  |  |

|     | No                  | 0x9000_0000                                       | USER BOOT               | OSPI0        |  |

|     |                     | 0x7000_0000                                       | USER BOOT               | OSPI1        |  |

| 0   | protection          | 0x2408_0000 ~ max RAM shared (ITCM/DTCM/AXI)      | SRAM BOOT (RAM shared)  | BOOT_ADDRESS |  |

|     | level<br>/          | 0x2400_0000~ max AXI<br>SRAM                      | SRAM BOOT (AXI<br>SRAM) | BOOT_ADDRESS |  |

|     | Low                 | 0x2000_0000                                       | SRAM BOOT (DTCM)        | 0x2000_0000  |  |

|     | protection<br>level | 0x0800_0000~max user<br>flash                     | USER BOOT               | BOOT_ADDRESS |  |

|     |                     | 0x0000_0000                                       | SRAM BOOT (ITCM)        | 0x0000_0000  |  |

|  | SCR | SPC[7:0] | BOOT_ADDRESS (configured in BOOT_ADDRx (x = 0,1)) | BOOT mode   | Boot address            |                       |

|--|-----|----------|---------------------------------------------------|-------------|-------------------------|-----------------------|

|  |     |          | 0x1FF0_0000                                       | SYSTEM BOOT | BootLoader              |                       |

|  |     |          |                                                   |             | USER BOOT               | 0X0800_0000 (when the |

|  |     |          | Others                                            | USER BOOT   | BOOT pin level is low)  |                       |

|  |     |          |                                                   | SYSTEM BOOT | BootLoader (When the    |                       |

|  |     |          |                                                   | 3131EW BOOT | BOOT pin level is high) |                       |

#### 2.2. Instruction of PMU use-related issues

Power consumption design is one of the most highlighted issues for GD32H7xx products. GD32H7xx allows the switch mode power supply low dropout regulator (SMPS low dropout regulator), USB power regulator, power-saving mode, and other features. Instructions are required for some issues that are worth attention when using specific functions.

#### 2.2.1. SMPS initialization configuration

The SMPS low dropout (LDO) regulator can be used to set the power supply of 0.9 V power domain. With different configurations, six valid power supply modes of 0.9V power domain can be achieved. Different power supply modes can make the chips more balanced in performance and power consumption. However, the following issues require attention in terms of SMPS configuration.

- Configuration of power supply mode must be prior to PLL configuration. PMU in default status can't drive application of high basic frequency or high load.

- Configuration of power supply mode should match external circuits. For example,

- When the external circuit is solely powered by SMPS, SMPS output is connected to VCORE to power V<sub>0.9V</sub> directly. If software configuration is such that LDO is powered by SMPS and powers V<sub>0.9V</sub>, SMPS will output 1.8 V or 2.5 V to V<sub>0.9V</sub> to burn out the chip.

- When the external circuit is so configured that LDO is powered by SMPS and powers V<sub>0.9V</sub> power domain, SMPS output will be connected to V<sub>DDLDO</sub> to power LDO. If the power supply mode solely by SMPS is configured for the software, LDO will be turned off which will cause power outage of V<sub>0.9V</sub>.

- Some packages don't have SMPS-related pins, so some power supply modes are not available. However, it is still required to configure LDO power supply mode or bypass mode before PLL configuration.

#### 2.2.2. **POR ON pin**

POR\_ON pin should be connected to VDD. Otherwise, after POR is reset, some registers may not in reset status.

#### 2.2.3. Programmer link issues in sleep mode

At present, the chip in sleep mode can not be downloaded or debugged through the programmer. It should exit from the sleep mode before being downloaded and debugged with the downloader.

#### 2.2.4. Pxx pin and Pxx\_C pin link issues in standby mode

Chips in standby mode can be awoken through the rising edge of WKUP pins. It is worth attention that WKUP pins of GD32H7xx have simulation input end. In other words, there are Pxy\_C and Pxy pin pairs. When the chip is in standby mode, Pxy\_C and Pxy pins will be short circuited.

#### 2.2.5. Software configuration

To correctly configure the PMU mode, users need to select the correct PMU mode in the firmware library system\_gd32h7xx.c to match the external circuit. For example, given that users use GD32H759I chip whose external circuit is powered by SMPS&LDO, to properly configure PMU to obtain 2.5 V SMPS output, users need to uncomment the codes in line 77 "#define SEL\_PMU\_SMPS\_MODE PMU\_SMPS\_2V5\_SUPPLIES\_LDO", as shown in the figure below.

```

system_gd32h7xx.c

62

Note: the power mode need to match the mcu selection and external power supply circuit.

63

· · · for iar project:

·····for·100-pin·mcu, need to define macro GD32H7XXV.

····· for 144-pin mcu, need to define macro GD32H7XXZ

····· for 176-pin mcu, need to define macro GD32H7XXI.

67

····for keil project:

68

·····do not need to define these macros extra.

\cdots \texttt{according} \cdot \texttt{to} \cdot \texttt{the} \cdot \texttt{selected} \cdot \texttt{mcu} \cdot \texttt{and} \cdot \texttt{external} \cdot \texttt{power} \cdot \texttt{supply} \cdot \texttt{circuit} \cdot \texttt{to} \cdot \texttt{uncomment}

71

the following macro SEL_PMU_SMPS_MODE.

72

73 ☐ #if ·defined(GD32H7XXI)

//#define SEL_PMU_SMPS_MODE PMU_LDO_SUPPLY

74

//#define SEL_PMU_SMPS_MODE · · · PMU_DIRECT_SMPS_SUPPLY

76

//#define SEL PMU SMPS MODE · · · PMU SMPS 1V8 SUPPLIES LDO

#define SEL_PMU_SMPS_MODE - PMU_SMPS_2V5_SUPPLIES_LDO

//#define SEL_PMU_SMPS_MODE · PMU_SMPS_1V8_SUPPLIES_EXT_AND_LDO

79

//#define SEL PMU_SMPS_MODE · · · PMU_SMPS_2V5_SUPPLIES_EXT_AND_LDO

80

//#define SEL PMU SMPS MODE PMU SMPS 1V8 SUPPLIES EXT

//#define SEL PMU_SMPS_MODE · · · PMU_SMPS_2V5_SUPPLIES_EXT

//#define SEL_PMU_SMPS_MODE · · · PMU_BYPASS

81

#elif defined(GD32H7XXZ) | defined(GD32H7XXV)

//#define SEL_PMU_SMPS_MODE · · · PMU_LDO_SUPPLY

//#define SEL_PMU_SMPS_MODE · · · PMU_BYPASS

85

```

#### 2.3. Instruction of RCU use

Some peripheral clocks can be configured to allow the user to select required clock for configuration. However, before configuring peripheral clocks, users should ensure that the corresponding clock is stable and running. For peripheral devices that support clock dynamic switch, user should ensure that the target clock has been stable before being switched. The

configurable peripheral clocks are as below.

- 1. ADC clock can be obtained by dividing the frequency of PLL1P, PLL2R, CK\_PER, or AHB clock by 2, 4, 6, 8, 10, 12, 14, and 16.

- The clock of TRNG can be selected as CK\_PLL0Q, CK\_PLL2P or IRC48M. The TRNG supports dynamic clock switch.

- The clock of USART can be selected as CK\_APBx (0, 1), CK\_AHB, CK\_LXTAL or CK IRC64MDIV. The USART supports dynamic clock switch.

- 4. The clock of I2C can be selected as CK\_APB1, CK\_PLL2R, CK\_IRC64MDIV or CK\_LPIRC4M. The I2C supports dynamic clock switch.

- The clocks of SPI0 (I2S0), SPI1 (I2S1), and SPI2 (I2S2) can be selected as CK\_PLL0Q, CK\_PLL1P, CK\_PLL2P, I2S\_CKIN or CK\_PER. The SPI0(I2S0), SPI1(I2S1) and SPI2(I2S2) support dynamic clock switch.

- The clocks of SPI3 and SPI4 can be selected as CK\_APB2, CK\_PLL1Q, CK\_PLL2Q, CK\_IRC64MDIV, CK\_LPIRC4M or CK\_HXTAL. The SPI3/SPI4 supports dynamic clock switch.

- The clock of SPI5 (I2S5) can be selected as CK\_APB2, CK\_PLL1Q, CK\_PLL2Q, CK\_IRC64MDIV, CK\_LPIRC4M, CK\_HXTAL or I2S\_CKIN. The SPI5/I2S5 supports dynamic clock switch.

- 8. The clock of LPDTS can be selected as CK APB4 or CK LXTAL.

- 9. The clock of CAN can be selected as CK\_HXTAL, CK\_APB2, CK\_APB2/2 or CK\_IRC64MDIV. The CAN supports dynamic clock switch.

- 10. The clock of RSPDIF can be selected as CCK\_PLL0Q, CK\_PLL1R, CK\_PLL2R or CK\_IRC64MDIV. The RSPDIF supports dynamic clock switch.

- 11. The clock of SAI2 can be selected as CK\_PLL0Q, CK\_PLL1P, CK\_PLL2P, I2S\_CKIN, CK\_PER or CK\_RSPDIF\_SYMB. The SAI2 supports dynamic clock switch.

- 12. The clocks of SAI0 and SAI1 can be selected as CK\_PLL0Q, CK\_PLL1P, CK\_PLL2P, I2S CKIN or CK PER. The SAI0 and SAI1 support dynamic clock switch.

- 13. The clock of HPDF can be selected as CK\_AHB or CK\_APB2. The HPDF supports dynamic clock switch.

- 14. The clock of HPDF\_AUDIO can be selected as CK\_PLL0Q, CK\_PLL1P, CK\_PLL2P, I2S CKIN or CK\_PER.

- The clock of EXMC can be selected as CK\_AHB, CK\_PLL0Q, CK\_PLL1R or CK\_PER.

The EXMC supports dynamic clock switch.

- The clock of SDIO can be selected as CK\_PLL0Q and CK\_PLL1R. The SDIO supports dynamic clock switch.

- 17. The clock of RTC can be selected as LXTAL clock, IRC32K clock, or HXTAL clocks divided by 2-63.

### 2.4. Monitoring junction temperature

During operation of chips, excessively high or low PN junction temperature will lead to declination of performance or even cause damage to the chips in more serious cases.

#### 2.4.1. Two methods for monitoring junction temperature

GD32H7xx can have junction temperature monitored in two ways, including reading the value of ADC high precision temperature senor or temperature monitor in PMU (JTM alarm function).

#### 2.4.2. Method for monitoring junction temperature with ADC

Real-time junction temperature can be monitored with ADC high precision temperature sensor. Detailed processes are as below:

- Configure conversion sequence and sampling time (t<sub>s\_temp</sub> us) of the temperature sensor channel (ADC2\_CH20). For typical value of t<sub>s\_temp</sub>, please refer to the datasheet.

- 2. Set TSVEN2 bit of ADC\_CTL1 register to enable the temperature sensor.

- 3. Set ADCON bit of ADC CTL1 register, or externally trigger ADC to convert.

- 4. Read the temperature sensor data V<sub>temperature</sub> from ADC data register, and calculate the actual temperature by using the following formula:

Temperature (°C) =

$$\{(V_{temperature} - V_{25}) / Avg\_Slope\} + 25$$

V<sub>25</sub>: internal temperature sensor output voltage at 25°C. For the typical value, please refer to the datasheet.

Avg\_Slope: Average Slope for curve between Temperature vs. V<sub>temperature</sub>, the typical value please refer to the datasheet.

#### 2.4.3. JTM alarm function

When VBTMEN bit of PMU\_CTL1 register is set, monitoring of temperature threshold will be initiated. Junction temperature is monitored by comparing high and low temperature thresholds. TEMPH and TEMPL signs in PMU\_CTL1 register can indicate whether the instrument temperature is higher or lower than the threshold. In addition, TEMPH and TEMPL wake-up suspension can be used for RTC to trigger signal.

#### 2.4.4. Advices for high-temperature and high-speed conditions

When chips run at high speed or high temperature, it is necessary to monitor junction temperature and JTM suspension in real time. If they are over thresholds, it is required to lower clock frequency.

#### 2.5. Use of Secure JTAG

Secure JTAG function is only applicable to JTAG interfaces rather than SWD interfaces. In addition, the debugging interface is irreversibly switched from SWD interface to JTAG interface because the switch achieved by modifying EFUSE can't be modified once it is written into EFUSE.

The method of switching SWD debugging interface to normal JTAG interface:

Modify JTAGNSW and NDBG[1:0] bit fields of user control register (EFUSE\_USER\_CTL) of EFUSE module to 1 and 00 respectively. After the power supply is reset, only JTAG interface can be found.

The method of switching SWD debugging interface to secure JTAG interface:

When configuring as secure JTAG interface for debugging, it is required to configure the user key which should be used for unlocking when this method is used. Modify JTAGNSW and NDBG bit fields of user control register (EFUSE\_USER\_CTL) of EFUSE module and EFUSE\_DP0 and EFUSE\_DP0 of password register by writing security key into DP0[31:0] and DP1[31:0] and modifying JTAGNSW to 1 and NDBG[1:0] to 01. After the power supply is reset, JTAG interface can not be found. In such case, the host computer should send key to MCU with scripts.

How to use scripts:

First create SecureJTAG. JlinkScript file and copy the contents below to the file:

```

int InitTarget(void)

{

int v;

int v1;

int v2;

int v3;

int v4;

JLINK_CORESIGHT_Configure("IRPre=0;DRPre=0;IRPost=0;DRPost=0;IRLenDevice=5");

JLINK_JTAG_Reset();

JLINK JTAG WriteIR(0x15);

JLINK JTAG StartDR();

JLINK_JTAG_WriteDRCont(0xfffffff, 32);

JLINK_SYS_Report("Writting secure jtag key1.....");

JLINK JTAG WriteDREnd(0x11223344, 32);

JLINK_JTAG_WriteIR(0x16);

JLINK JTAG StartDR();

JLINK_JTAG_WriteDRCont(0xfffffff, 32);

JLINK_SYS_Report("Writting secure jtag key2.....");

JLINK_JTAG_WriteDREnd(0x55667788, 32);

JLINK_JTAG_WriteIR(0x18);

JLINK JTAG StartDR();

JLINK_SYS_Report("Reading secure jtag key1.....");

```

```

JLINK_JTAG_WriteDREnd(0xfffffff, 32);

v1 = JLINK_JTAG_GetU32(0);

JLINK SYS Report1("secure jtag key1:", v1);

JLINK_JTAG_WriteIR(0x19);

JLINK_JTAG_StartDR();

JLINK_SYS_Report("Reading secure jtag key2.....");

JLINK_JTAG_WriteDREnd(0xfffffff, 32);

v2 = JLINK_JTAG_GetU32(0);

JLINK_SYS_Report1("secure jtag key2:", v2);

JLINK_JTAG_WriteIR(0x1e);

JLINK_JTAG_StartDR();

JLINK_SYS_Report("Reading boundary scan ID.....");

JLINK_JTAG_WriteDREnd(0xfffffff, 32);

v3 = JLINK_JTAG_GetU32(0);

JLINK_SYS_Report1("boundary scan ID:", v3);

JLINK JTAG WriteIR(0x1a);

JLINK_JTAG_StartDR();

JLINK_SYS_Report("Reading secure jtag state....");

JLINK_JTAG_WriteDREnd(0xfffffff, 32);

v4 = JLINK_JTAG_GetU32(0);

JLINK_SYS_Report1("secure jtag state:", v4);

return 0;

```

0X11223344 in the file is the value written into DP0[31:0] when users set the key. 0X55667788 is the value written into DP1[31:0] when users set the key. 0x15 and 0x16 commands in the file represent commands of writing keys. 0x18 and 0x19 commands represent reading written keys. 0X1e command represents reading mcu device ID. 0X1a command represents reading the status of secure jtag and wrong\_seq signs.

Then create secure JTAG.bat file in the same path as that of SecureJTAG1.JlinkScript and copy the contents below to the file:

```

PATH=%PATH%;D:\Keil_v528\ARM\Segger;

jlink.exe -JLinkScriptFile SecureJTAG1.JlinkScript -device Cortex-M7 -if JTAG -speed 100 -

autoconnect 1 -JTAGConf -1,-1

pause

```

D:\Keil\_v528\ARM\Segger is the directory of jlink.exe.

Finally, execute secureJTAG.bat and JTAG debugging is unlocked and ready to use.

#### Note:

- 1. If the password is entered in error, it is required to reset the power supply.

- 2. If there is any error in entering the sequence, it is required to reset the power supply for decryption.

- 3. Entering correct password to open debugging only applies to SPC\_L or below. ROM, RAM secure access mode, and SPC\_H would not be opened through this operation.

### 2.6. Jlink debug issues

When debugging GD32H7XX chips with KEIL IDE, if address memory interface driven by EXMC is initiated in the course, KEIL IDE will be stuck when the interface is opened again and it is required to reset window settings.

#### 2.7. Instruction of cache use

#### 2.7.1. Data consistency issues when using Dcache and DMA simultaneously

GD32H7xx provides high-speed cache that allows read assignment. When cache is not hit, data will be assigned with high-speed cache lines and 32-byte data is saved from the master storage to the cache. Subsequently, when accessing these master storage addresses, cache will be hit to read the data directly. When cache is enabled on SRAM, there will be some consistency-related issues when CPU and DMA access SRAM simultaneously.

CPU reads the data DMA writes into SRAM.

When DMA reads data from peripheral and updates into the receive buffer destination[] in SRAM, CPU attempts to read the data in destination[]. It will read the existing data in cache rather than new data in SRAM.

Solutions are as below:

After DMA receives data, conduct invalid operation on destination[] in cache. destination[] in cache will be invalid through the operation below. When CPU attempts to read destination[], cache will not be hit.

```

····/*·invalidate·the·cache·line·*/

····SCB_InvalidateDCache_by_Addr((uint32_t *) destination, BUFFER_SIZE·*·2);

```

To ensure that cache line margins are aligned, destination[] must be 32 bytes aligned.

```

__attribute__((aligned(32))) uint16_t destination[BUFFER_SIZE];

```

DMA reads the data CPU writes into SRAM.

When CPU is updating the data to be transmitted in the transmit buffer welcome[], it will update the data in cache only rather than the data in SRAM. When DMA reads the data in welcome[], it will read the data from SRAM rather than new data in cache updated by CPU.

Solutions are as below:

1. Before initiating DMA transmission, it is required to clear cache and refresh welcome[] in cache to SRAM.

```

'/* clean the cache lines */

SCB_CleanDCache_by_Addr((uint32_t *) welcome, BUFFER_SIZE);

'/* configure DMA1 */

dma_config();

```

2. The address saved in welcome[] must be 32 bytes aligned.

```

__attribute__((aligned(32))) ·uint8_t ·welcome[BUFFER_SIZE] ·= ·"Hi, ·this ·is ·an ·example: ·RAM_TO_USART ·by ·DMA ·!\n";

```

#### 2.7.2. Use of cache and data alignment configuration

The table below lists some ARM CMSIS Dcache operating functions recommended on the official website.

Table 2-2. API for cache operation

| API for cache operation                                               | Description                                                 |

|-----------------------------------------------------------------------|-------------------------------------------------------------|

| void SCB_EnableDCache (void)                                          | After invalidating the whole data cache, enable data cache. |

| void SCB_DisableDCache (void)                                         | After cleaning the whole data cache, disable data cache.    |

| void SCB_CleanDCache(void)                                            | Clean the whole data cache.                                 |

| void SCB_CleanDCache_by_Addr (uint32_t *addr, int32_t dsize)          | Clean data cache lines by address.                          |

| void SCB_InvalidateDCache(void)                                       | Invalidate the whole data cache.                            |

| void SCB_InvalidateDCache_by_Addr (uint32_t * addr, int32_t dsize )   | Invalidate data cache lines by address.                     |

| void SCB_CleanInvalidateDCache(void)                                  | Clean and invalidate the whole data cache.                  |

| void SCB_CleanInvalidateDCache_by_Addr(uint32_t *addr, int32_t dsize) | Clean and invalidate data cache lines by address.           |

**Note:** Since the data cache line has 32 bytes and the cache is read and written in lines, addr must have 32 bytes with margin aligned and dsize must be an integer multiple of 32 bytes.

Cleaning cache aims to forcibly write lines marked as dirty (rewritten) in cache to SRAM, clean the sign of dirty lines, and rebuild consistency between cache and SRAM. This avoids failing to timely capture the latest data in cache when SRAM is read by DMA.

Invalidating cache aims to invalidate cache lines by clearing the significant bit in cache lines only rather than clearing the data in cache lines. This avoids CPU from capturing data in cache instead of the latest data after SRAM data is updated.

In addition, to avoid consistency issues, the Memory Protection Unit (MPU) can be used to define SRAM area shared by CPU and DMA as not using the data cache but keep SRAM which can only be accessed by CPU using the data cache. For this method, please refer to

MPU configuration use document of ARM.

#### 2.8. Use of CAN filter

The CAN bus controller is integrated with a flexibly configured mailbox system for sending and receiving CAN frame. The mailbox system consists of one set of mailboxes (maximumly 32 mailboxes) for storing control data, time stamps, message identifiers, and message data. Each CAN controller has 512-byte RAM space for configuration of mailbox or FIFO descriptor.

When receive FIFO is enabled in CAN, the RAM space occupied by the mailbox will be used for receiving FIFO descriptors. With the identifier filtering function, the receive FIFO can maximumly filter 104 extended identifiers, 208 standard identifiers, or 8 bits of 416 identifiers. Maximum 32 identifier filtering table elements can be configured through the private filtering register of receive FIFO/mailbox.

#### When Rx FIFO is disabled:

- If RPFQEN bit of CAN\_CTL0 register is 0, then CAN\_RMPUBF register is used for all receive mailboxes.

- If RPFQEN bit of CAN\_CTL0 register is 1, then CAN\_RFIFOMPFx (x = 0..31) register is used for receive mailboxes individually.

#### When Rx FIFO is enabled:

- If RPFQEN bit of CAN\_CTL0 register is 0, then CAN\_RMPUBF register is used for all receive mailboxes, and CAN\_RFIFOPUBF and CAN\_RFIFOMPFx (x = 0..31) registers are used to configure all Rx FIFO identifier filtering table elements. Values of all these registers must be configured the same.

- If RPFQEN bit of CAN\_CTL0 register is 1, then CAN\_RFIFOMPFx (x=0..31) register is used to configure Rx FIFO identifier filtering table elements set by RFFN[3:0] bit field of CAN\_CTL2 register and receive mailboxes (as descriptors of receive mailboxes and Rx FIFO can not occupy RAM of the same area at the same time, a set of registers are used to configure filtering data under separate control), and CAN\_RFIFOPUBF register is used to configure all remaining Rx FIFO identifier filtering table elements.

Configuration of the number of Rx FIFO identifier filtering table elements is as listed in the table below:

| RFFN[3:0] | Number of Rx FIFO identifier filtering table elements | Space occupied by Rx<br>FIFO | Mailbox available |

|-----------|-------------------------------------------------------|------------------------------|-------------------|

| 0000      | 8                                                     | Mailbox descriptor 0 - 7     | Mailbox 8- 31     |

| 0001      | 16                                                    | Mailbox descriptor 0 - 9     | Mailbox 10- 31    |

| 0002      | 24                                                    | Mailbox descriptor 0 - 11    | Mailbox 12- 31    |

| 0003      | 32                                                    | Mailbox descriptor 0 - 13    | Mailbox 14- 31    |

| 0004      | 40                                                    | Mailbox descriptor 0 - 15    | Mailbox 16- 31    |

| RFFN[3:0] | Number of Rx FIFO identifier filtering table elements | Space occupied by Rx<br>FIFO | Mailbox available |

|-----------|-------------------------------------------------------|------------------------------|-------------------|

| 0005      | 48                                                    | Mailbox descriptor 0 - 17    | Mailbox 18- 31    |

| 0006      | 56                                                    | Mailbox descriptor 0– 19     | Mailbox 20- 31    |

| 0007      | 64                                                    | Mailbox descriptor 0–21      | Mailbox 22- 31    |

| 8000      | 72                                                    | Mailbox descriptor 0– 23     | Mailbox 24- 31    |

| 0009      | 80                                                    | Mailbox descriptor 0– 25     | Mailbox 26- 31    |

| 000A      | 88                                                    | Mailbox descriptor 0–27      | Mailbox 28- 31    |

| 000B      | 96                                                    | Mailbox descriptor 0– 29     | Mailbox 30- 31    |

| 000C      | 104                                                   | Mailbox descriptor 0-31      | None              |

| Others    | 104                                                   | Mailbox descriptor 0 - 31    | None              |

By taking RFFN[3:0] = 3 as an example, at this time, the number of Rx FIFO identifier filtering table elements is 32, the space of mailbox descriptor 0-13 is occupied by FIFO descriptor, and the remaining mailboxes14-31 can be used for sending and receiving for mailbox. There are three formats for Rx FIFO identifier filtering table elements, which can be configured by FS[1:0] bit field of CAN\_CTL0 register. When FS[1:0] is 0, Rx FIFO identifier filtering table elements are in format A and allow maximum 32 complete standard or extended identifiers. When FS[1:0] is 1, they are in format B and allow maximum 64 complete standard or 14 bits of extended identifiers. When FS[1:0] is 2, they are in format C and allow maximum 128 complete standard or 8 bits of extended identifiers.

Configuration of the format of Rx FIFO identifier filtering table elements is as below:

The Rx FIFO identifier filtering table elements configured in format B allows 64 complete standard or 14 bits of extended identifiers.

```

can_fifo_parameter.filter_format_and_number = CAN_RXFIFO_FILTER_B_NUM_64;

/* used for 26-63nd IDs filtering configuration */

can_fifo_parameter.fifo_public_filter = 0xFFFFFFFF;

can_rx_fifo_config(CANO, &can_fifo_parameter);

```

Because FS[1:0] is 3 and mailboxes 0-13 are occupied by FIFO, private filters 0-13 of receive FIFO/mailbox are used to receive and filter FIFO. The code configuration is as below:

```

for(i=0; i<=13; i++) {

can_private_filter_config(CAN0, i, 0xfffffffff);

}</pre>

```

# 2.9. Hardfault issue arising from non-aligned access to EXMC SDRAM

In default situation, when access property of SDRAM has not been modified, hardfault will occur when accessing SDRAM in non-aligned way for 0xC0000000-0xDFFFFFF defaults to device type and does not allow non-aligned access. For details, please refer to the table below.

#### Table2-3. ARMv7-M address mapping

| Address                  | Name       | RAM type (s)                 | XN | Cache | Description/ supported storage                                 |

|--------------------------|------------|------------------------------|----|-------|----------------------------------------------------------------|

| 0xE0000000-<br>0xFFFFFFF | System     | Device & Strongly<br>Ordered | XN | -     | Vendor system region (VENDOR_SYS) Private Peripheral Bus (PPB) |

| 0xC0000000-<br>0xDFFFFFF | Device     | Device                       | XN | -     | Non-shareable memory                                           |

| 0xA0000000-<br>0xBFFFFFF | Device     | Device, Shareable            | XN | -     | Shareable memory                                               |

| 0x80000000-<br>0x9FFFFFF | RAM        | Normal                       | -  | WT    | Memory with WT cache attributes                                |

| 0x60000000-<br>0x7FFFFFF | RAM        | Normal                       | -  | WBWA  | Write-back, Write-allocate L2/L3                               |

| 0x40000000-<br>0x5FFFFFF | Peripheral | Device                       | XN | -     | On-chip peripheral address space                               |

| 0x20000000-<br>0x3FFFFFF | SRAM       | Normal                       | -  | WBWA  | SRAM<br>On-chip RAM                                            |

| 0x00000000-<br>0x1FFFFFF | Code       | Normal                       | -  | WT    | ROM<br>Flash Memory                                            |

To access SDRAM in non-aligned way, it is required to modify the type of the address space where SDRAM is located with MPU, like the same type as that of RAM. For example, users can configure Write Through property for 0xC0000000.

```

mpu_region_init_struct mpu_init_struct;

mpu_region_struct_para_init(&mpu_init_struct);

/* disable the MPU */

ARM MPU Disable();

ARM_MPU_SetRegion(0, 0);

/* configure the MPU attributes for SDRAM */

mpu_init_struct.region_base_address = 0xC0000000;

mpu_init_struct.region_size

= MPU_REGION_SIZE_32MB;

mpu_init_struct.access_permission = MPU_AP_FULL_ACCESS;

= MPU ACCESS NON BUFFERABLE;

mpu init struct.access bufferable

mpu_init_struct.access_cacheable

= MPU_ACCESS_CACHEABLE;

mpu_init_struct.access_shareable

= MPU_ACCESS_NON_SHAREABLE;

mpu_init_struct.region_number

= MPU_REGION_NUMBER0;

mpu_init_struct.subregion_disable

= MPU_SUBREGION_ENABLE;

= MPU_INSTRUCTION_EXEC_PERMIT;

mpu_init_struct.instruction_exec

= MPU_TEX_TYPE0;

mpu_init_struct.tex_type

mpu region config(&mpu init struct);

mpu_region_enable();

```

/\* enable the MPU \*/

ARM\_MPU\_Enable(MPU\_MODE\_PRIV\_DEFAULT);

#### 2.10. Precautions for SAI using DMA burst transfer to send data

Each audio sub-module of GD32H7xx SAI has an 8-byte FIFO and DMA interface. Enabling DMA access is configured with DMA enable bit (DMAEN) of SAI\_BxCFG0 register. DMA request and FIFO request (FFREQ) are generated together. The generation status of FIFO request depends on FIFO threshold (FFTH) and FIFO status (FFSTAT), which is important when using DMA burst transfer.

The table below lists the recommended relationship between DMA burst transfer and SAI FIFO threshold.

| DMA transfer width | DMA burst transfer type  | SAI data width | SAI FIFO threshold                      |  |

|--------------------|--------------------------|----------------|-----------------------------------------|--|

|                    | Single                   |                | Empty, 1/4 full, half-full, or 3/4 full |  |

| 16                 | 4-beat incremental burst | 16             | Empty or 1/4 full                       |  |

|                    | transfer                 |                | Empty of 1/4 full                       |  |

|                    | Single                   |                | Empty, 1/4 full, half-full, or 3/4 full |  |

| 32                 | 4-beat incremental burst | 32             | Empty or 1/4 full                       |  |

|                    | transfer                 |                | Empty or 1/4 full                       |  |

When the audio sub-module is configured in transmitting mode, FIFO threshold must be set as a designated value to ensure that there is enough remaining space to achieve a complete DMA burst writing in the worst situation. Otherwise, FIFO overflow error might happen. When the audio sub-module is configured in receiving mode, FIFO threshold must be set as a designated value to ensure that there is enough remaining space to achieve a complete DMA burst reading in the worst situation to prevent FIFO underflow error.

# 2.11. Enabling situation of ENET cache

ENET module uses DMA mechanism while cache of ENET module is enabled. Due to high data traffic, ENET module will update RAM through DMA rapidly, which may lead to inconsistency between the data captured by DMA and the data in cache.

Therefore, we first need to specify the address of the relevant memory area, including the ENET RxDMA /TxDMA descriptor, LWIP RAM heap, and transmit / receive buffer.

```

### defined (GO32FYXX)

### de

```

```

/*·Relocate·the·LwIP·RAM·heap·pointer·*/

#define·LWIP_RAM_HEAP_POINTER····(0x30004000)

```

In addition, we need to set cache access permit of the RAM area in use with MPU module as no buffer and no cache to ensure real-time property and accuracy of data.

```

void mpu config(void)

mpu_region_init_struct mpu_init_struct;

mpu region struct para init(&mpu init struct);

····/*·disable·the·MPU·*/

ARM MPU SetRegion(OU, OU);

···/* Configure the DMA descriptors and Rx/Tx buffer*/

mpu_init_struct.region_base_address = 0x30000000;

mpu_init_struct.region_size = MPU_REGION_SIZE 16KB;

mpu_init_struct.access_permission = MPU_AP_FULL_ACCESS;

mpu_init_struct.access_bufferable = MPU_ACCESS_BUFFERABLE;

mpu_init_struct.access_cacheable = MPU_ACCESS_NON_CACHEABLE;

mpu_init_struct.access_shareable = MPU_ACCESS_NON_SHAREABLE;

mpu_init_struct.region_number = MPU_REGION_NUMBER0;

...mpu_init_struct.subregion_disable = MPU_SUBREGION_ENABLE;

...mpu_init_struct.instruction_exec = MPU_INSTRUCTION_EXEC_PERMIT;

mpu init_struct.tex type = MPU TEX_TYPE0;

mpu_region_config(&mpu_init_struct);

···mpu_region_enable();

···/* ·Configure · the ·LwIP · RAM · heap · */

mpu_init_struct.region_base_address = 0x30004000;

mpu_init_struct.region_size = MPU_REGION_SIZE_16KB;

mpu_init_struct.access_permission = MPU_AP_FULL_ACCESS;

mpu_init_struct.access_bufferable = MPU_ACCESS_NON_BUFFERABLE;

mpu init struct.access cacheable = MPU ACCESS NON CACHEABLE;

mpu_init_struct.access_shareable = MPU_ACCESS_SHAREABLE;

mpu_init_struct.region_number = MPU_REGION_NUMBER1;

mpu init struct.subregion disable = MPU SUBREGION ENABLE;

mpu_init_struct.instruction_exec = MPU_INSTRUCTION_EXEC_PERMIT;

mpu init struct.tex type = MPU TEX TYPE1;

mpu region config(&mpu init struct);

mpu region enable();

·/*·enable·the·MPU·*/

ARM MPU_Enable (MPU_MODE_PRIV_DEFAULT);

```

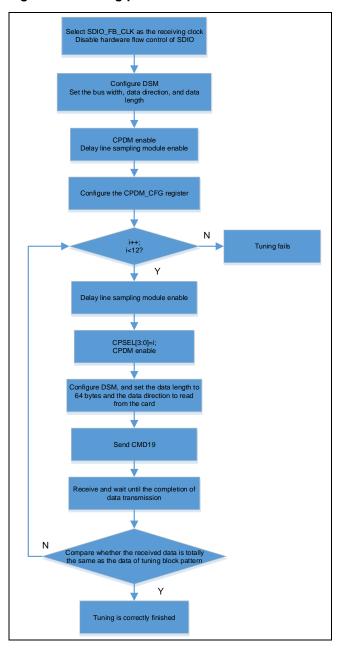

At the same time, it is required to select the set RAM area in related project settings. Otherwise, the above configuration will be invalid.

### 2.12. Precautions for Bootloader operation

For details, please refer to Precautions for AN126 GD32H7xx BootLoader Operations.

#### 2.13. Precautions for the Use of USBHS

For details, please refer to Precautions for the Use of USBHS of AN117 GD32H7xx Series.

#### 2.14. Precautions for the Use of SDIO

#### 2.14.1. SDIO clock configuration

CK\_SDIO is a kernel clock of SDIO module. SDIO\_CLK provided to SD/eMMC card is obtained through frequency division of the clock. When configuring CK\_SDIO through RCU, it is recommended to configure the frequency of the working clock CK\_SDIO to up to 208 Mhz.

When configuring AF function with pins, it is recommended to modify GPIOx\_AFSELx(x=0, 1) first and then switching GPIO mode into AF.

#### 2.14.2. SDIO power-on initialization

#### Power-on initialization and voltage switch of UHS-I SD card

SD 3.0 card allows UHS-I (Ultra High Speed Bus Speed Mode phase I) speed mode, including SDR12, SDR25, SDR50, SDR104, and DDR50. The card works in UHS-I at 1.8 V while the card is powered on at 3.3 V, so UHS-I mode allows the voltage switch from 3.3 V to 1.8 V. When the voltage switch sequence is completed successfully, SDR12 card will enter into UHS-I mode by default.

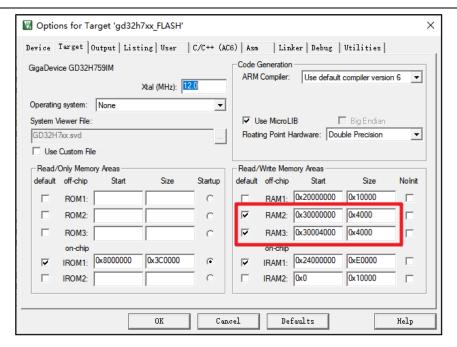

Power-on initialization of the card and capture of card status and information can be completed for cards that can work in UHS-I. When responding to ACMD41, the card will reply with the support of 1.8 V voltage switch and then proceed with 1.8 V voltage switch operation. Main processes are shown in the figure below. In addition, please note that SDIO0 can work in UHS-I but SDIO1 can not work in UHS-I. In other words, SDIO1 can not generate the chip signal to control external voltage switch.

Figure 2-1. Processes of power-on initialization and voltage switch of SD card

#### Power-on initialization of eMMC

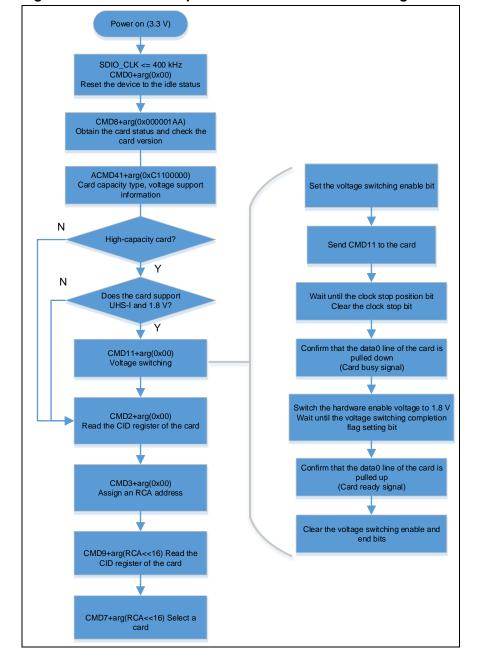

Power-on processes of eMMC are shown in the figure below. First, the host determines whether eMMC can work at 1.8 V with OCR register, and then the host will select 1.8 V to power on eMMC again.

Figure 2-2. Processes of power-on initialization and voltage switch of eMMC

#### 2.14.3. Bus width configuration

When the host sends a command to set device bus speed, it is required to change the width, speed mode, and DDR of the host after 64 byte-data is received.

After power-on initialization of SD card is completed, configuration of bus width and speed can be done by sending commands according to the table below. Please note that 1-bit bus is not allowed in UHS-I mode.

Table 2-4. Configuring bus width of SD card

| Selected width | Command | Parameters |

|----------------|---------|------------|

| 1bit           | ACMD6   | 0x00       |

| 4bit           | ACIVIDO | 0x02       |

Table2-5. Configuring bus speed of SD card

| Selected speed mode | Voltage/V | Command | Parameters |

|---------------------|-----------|---------|------------|

| SDR12               | 1.8       |         | 0x80FFFF00 |

| SDR25               | 1.8       |         | 0x80FFFF01 |

| SDR50               | 1.8       | CMD6    | 0x80FF1F02 |

| SDR104              | 1.8       |         | 0x80FF1F03 |

| DDR50               | 1.8       |         | 0x80FF1F04 |

After power-on initialization of eMMC is completed, configuration of bus width and speed can be done by sending commands according to the table below.

Table2-6. Configuring bus mode of eMMC

| Selected width | Command | Parameters |

|----------------|---------|------------|

| 1BIT SDR       |         | 0x03B70000 |

| 4BIT SDR       |         | 0x03B70100 |

| 8BIT SDR       | CMD6    | 0x03B70200 |

| 4BIT DDR       |         | 0x03B70500 |

| 8BIT DDR       |         | 0x03B70600 |

Table2-7. Configuring bus speed of eMMC

| 5 5 1               |           |         |            |

|---------------------|-----------|---------|------------|

| Selected speed mode | Voltage/V | Command | Parameters |

| DS                  | 1.8/3.3   |         | 0x03B90000 |

| HS                  | 1.8/3.3   | CMD6    | 0x03B90100 |

| HS200               | 1.8       |         | 0x03B90200 |

#### High-speed bus tuning of SD card

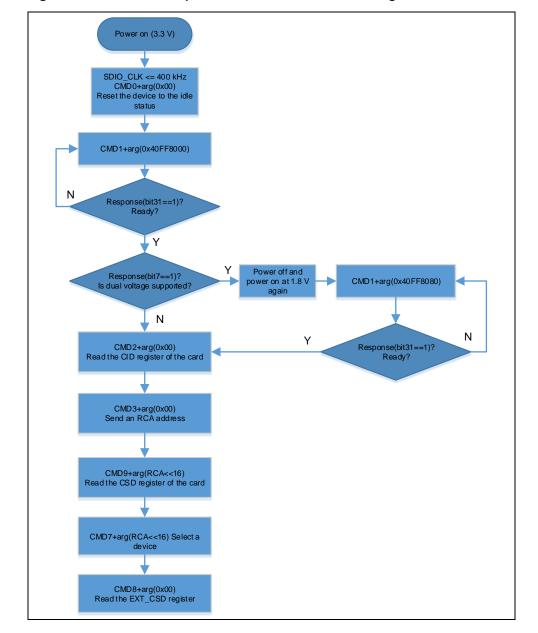

When SDR50 and SDR104 that can work in UHS-I is in bus speed mode, CPDM module can be used for tuning of sampling points of receiving data. After CPDM is used, it is required to disable hardware flow control. Before sending CMD19 for tuning, it is required to configure delay line length with CPDM.

Reference codes for configuring delay line length with CPDM are as below.

Figure 2-3. Tuning processes of SD card

#### 2.14.4. Accessing eMMC Boot partition data

eMMC has two Boot partitions in the same size, which is obtained by calculating EXT\_CSD register according to the calculation formula EXT\_CSD[226]\*128K byte. EXT\_CSD register is obtained by the host sending CMD8. Data reading and writing in Boot partition is the same as that in other partitions, but before sending reading and writing commands, the host should send CMD6 access to Boot partition. Detailed command is listed in the table below. The data written into Boot partition can be read automatically upon power-on initialization. Detailed operations are conducted according to protocols. Configuration of reading content bus of Boot partition is also required to be done according to protocols beforehand.

Table2-8. Accessing partition commands and parameters

| Switched partition | Command | Parameters |

|--------------------|---------|------------|

| User partition     |         | 0x03B30000 |

| Boot partition 1   | CMD6    | 0x03B30100 |

| Boot partition 2   |         | 0x03B30200 |

#### 2.14.5. MDMA configuration

#### Controlling SDIO transfer process with MDMA

When MDMA is not used, CPU will control SDIO transfer process. For example, after transferring multiple blocks of data, send CMD12 stop command. After one dual-buffer transfer in buffer is done, modify buffer address configuration in IDMA.

If MDMA is used, it can control SDIO transfer in place of CPU in three time periods, including the end of data transfer (SDIO\_DATA\_END), the end of command sequence (SDIO\_CMD\_END), and the end of buffer transfer (SDIO\_BUF\_END). When MDMA is triggered at these moments, it will transfer pre-configured static data to SDIO register to achieve SDIO control.

The flow chart below shows the example of MDMA controlling the sending of CMD12 after SDIO transfers multiple blocks of data.

Figure 2-4. Flow chart of MDMA controlling the sending of CMD12

In addition, MDMA supports the linked list, so it is possible to conduct transfer control on SDIO for many times with multi-node linked list.

#### Transferring data to DTCM/ITCM with MDMA

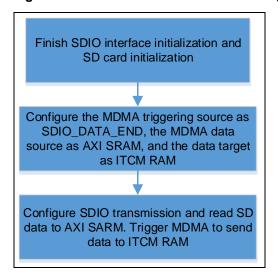

The figure below is an example of using SDIO and MDMA at the same time. It aims to configure SDIO\_DATA\_END as a source to trigger MDMA to transfer SD card data to ITCM.

Figure 2-5. Flow chart of MDMA controlling RAM data transfer

#### 2.14.6. IDMA configuration

There is DMA (IDMA) in SDIO which supports single buffer transfer and dual buffer transfer.

In single buffer transfer mode, it is only required to configure SDIO register SDIO\_IDMACTL in single buffer mode and enable IDMA before transfer so that single buffer transfer can be achieved with IDMA.

In dual buffer transfer mode, SDIO will read or write data in two buffers in turn. When SDIO is using one buffer, CPU can read or write data in the other buffer. It is required to configure SDIO register SDIO\_IDMACTL in dual buffer mode and enable IDMA, configure SDIO\_IDMASIZE as the buffer size, configure SDIO\_IDMAADDR0 and SDIO\_IDMAADDR1 as the addresses of the two external buffers, and choose to enable IDMAEND interruption. By enabling SDIO data transfer, SDIO will access two buffers in turn. When transfer is done in one buffer, IDMAEND interruption will be triggered, and CPU can access the other buffer that is not used by SDIO by judging it according to BUFSEL in SDIO\_IDMACTL.

# 3. Revision history

Table 3-1. Revision history

| Revision No. | Description     | Date        |

|--------------|-----------------|-------------|

| 1.0          | Initial release | May 9, 2023 |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which have been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as its suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as its suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2023 GigaDevice - All rights reserved