**GigaDevice Semiconductor Inc.**

# Methods to Reduce GD32L233 MCU Power Consumption

Application Note AN106

# **Table of Contents**

| Tab | ole o | f Contents                          | 1 |

|-----|-------|-------------------------------------|---|

| Lis | t of  | Figures                             | 2 |

| Lis | t of  | Tables                              | 3 |

| 1.  | Intr  | oduction                            | 4 |

| 2.  | Red   | duce power consumption of GD32L233  | 5 |

| 2   | 1.    | Power supply architecture           | 5 |

| 2   | 2.    | Power-saving modes                  | 6 |

| 2   | .3.   | Methods to reduce power consumption | 7 |

| 3.  | Su    | nmary1                              | 0 |

| 4.  | Rev   | vision history1                     | 1 |

|     |       |                                     |   |

# **List of Figures**

```

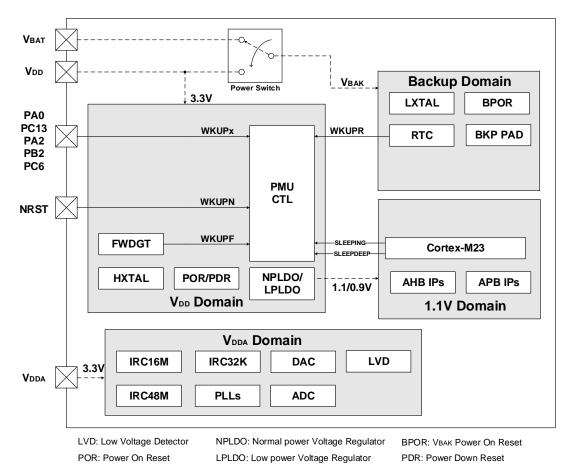

Figure 2-1. Power supply overview......5

```

# **List of Tables**

| Table 2-1. Power saving mode summary | . 6 |

|--------------------------------------|-----|

| Table 4-1. Revision history          | .11 |

# 1. Introduction

The GD32L233 family of devices is a 32-bit general-purpose microcontroller based on an Arm<sup>®</sup> Cortex<sup>®</sup>-M23 core with ultra-low power consumption. Its power module has a variety of power saving modes especially suitable for low power applications. This application note mainly provides a method to reduce power consumption for GD32L233 devices.

# 2. Reduce power consumption of GD32L233

# 2.1. Power supply architecture

Power consumption design is one of the most important issues of GD32L233 series products. The power management unit provides ten power saving modes that reduce power consumption and allow applications to strike the best compromise between CPU uptime requirements, speed, and power consumption. As shown in *Figure 2-1. Power supply overview*. Power Domain overview, the GD32L233 series device has three power domains, including the V<sub>DD</sub> / V<sub>DDA</sub> domain, 1.1V domain, and backup domain. The V<sub>DD</sub> / V<sub>DDA</sub> domain is directly powered by the power supply. The LDO is embedded in the V<sub>DD</sub> / V<sub>DDA</sub> domain to power the 1.1V domain. There is a power switch in the backup domain, and when the V<sub>DD</sub> power is off, the power switch can switch the power of the backup domain to the V<sub>BAT</sub> pin, at which point the backup domain is powered by the V<sub>BAT</sub> pin (battery).

### Figure 2-1. Power supply overview

# 2.2. Power-saving modes

After system reset or power reset, GD32L233 MCU is in full function state and all power domains are in power supply state. At this point, there are three ways to achieve lower power consumption: Slow down the system clock (HCLK, PCLK1 and PCLK2), turn off the clock of unused peripherals, in addition, ten power saving modes can achieve lower power consumption, they are Run mode, Run mode 1, Run mode 2, Sleep mode, Sleep mode 1, Sleep mode 2, Deep sleep mode, Deep sleep mode 1, Deep sleep Mode 2 and Standby mode. The wake up time of low power mode contributes a lot to power optimization and application flexibility, so the trade-off between low power mode consumption and the corresponding wake up time must be made.

|                  |                                                                                                | J                                                                   |                                                   |                                                                                                                    | Wakeup               | Wakeup                 |

|------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|------------------------|

| Mode             | Description                                                                                    | LDO                                                                 | Entry                                             | Wakeup                                                                                                             | status               | Latency                |

| Run              | no effect on all clocks,<br>all power on                                                       | NPLDO on<br>LPLDO on                                                | system / power<br>reset or wakeup<br>from standby | -                                                                                                                  | -                    | -                      |

| Run1             | system clock <=<br>16Mhz                                                                       | NPLDO on<br>LPLDO on                                                | LDOVS set to<br>0.9V                              | clear LDVOS                                                                                                        | -                    | -                      |

| Run2             | system clock <= 2Mhz                                                                           | NPLDO in low<br>driver mode<br>LPLDO on                             | LDOVS set to<br>0.9V and<br>LDNP set to 1         | clear LDVOS and<br>LDNP                                                                                            | -                    | -                      |

| Sleep            | Only CPU clock is off                                                                          | NPLDO on<br>LPLDO on                                                | SLEEPDEEP =<br>0,WFI or WFE<br>from Run           | Any interrupt for WFI<br>Any event (or interrupt<br>when SEVONPEND<br>is 1) for WFE                                | Run mode             | -                      |

| Sleep1           | Only CPU clock is off                                                                          | NPLDO on<br>LPLDO on                                                | SLEEPDEEP =<br>0,WFI or WFE<br>from Run1          | Any interrupt for WFI<br>Any event (or interrupt<br>when SEVONPEND<br>is 1) for WFE                                | Run1 mode            | -                      |

| Sleep2           | Only CPU clock is off                                                                          | NPLDO in low<br>driver mode<br>LPLDO on                             | SLEEPDEEP =<br>0,WFI or WFE<br>from Run2          | Any interrupt for WFI<br>Any event (or interrupt<br>when SEVONPEND<br>is 1) for WFE                                | Run2 mode            | -                      |

| Deep-<br>sleep   | 1. All clocks in the<br>1.1V domain are off<br>2. Disable IRC16M,<br>IRC48M, HXTAL and<br>PLLs | NPLDO in low<br>driver mode or<br>normal driver<br>mode<br>LPLDO on | SLEEPDEEP =<br>1, LPMOD = 00,<br>WFI or WFE       | Any interrupt from<br>EXTI lines for WFI<br>Any event(or interrupt<br>when SEVONPEND<br>is 1) from EXTI for<br>WFE | / Run2               | + Flash<br>wakeup time |

| Deep-<br>sleep 1 | 1. All clocks in the<br>1.1V domain are off                                                    | NPLDO off<br>LPLDO on                                               | SLEEPDEEP =<br>1, LPMOD = 01,                     | Any interrupt from<br>EXTI lines for WFI                                                                           | Run / Run1<br>/ Run2 | IRC16M<br>wakeup time, |

### Table 2-1. Power saving mode summary

# AN106 Methods to Reduce GD32L233 MCU Power Consumption

| Mode    | Description              | LDO                    | Entry                                       | Wakeup                 | Wakeup     | Wakeup                   |

|---------|--------------------------|------------------------|---------------------------------------------|------------------------|------------|--------------------------|

| Mode    | Description              | LDO                    | Entry                                       | Wakeup                 | status     | Latency                  |

|         | 2. Disable IRC16M,       |                        | WFI or WFE                                  | Any event(or interrupt |            | + NPLDO                  |

|         | IRC48M, HXTAL and        |                        |                                             | when SEVONPEND         |            | wakeup                   |

|         | PLLs                     |                        |                                             | is 1) from EXTI for    |            | time+Flash               |

|         | 3. LPLDO instead of      |                        |                                             | WFE                    |            | wakeup time              |

|         | NPLDO                    |                        |                                             |                        |            |                          |

|         | 1. All clocks in the     |                        |                                             |                        |            |                          |

|         | 1.1V domain are off      |                        |                                             |                        |            |                          |

|         | 2. Disable IRC16M,       | XTAL and               |                                             | Any interrupt from     |            | IRC16M                   |

|         | IRC48M, HXTAL and        |                        | SLEEPDEEP =                                 | EXTI lines for WFI     |            | wakeup time,             |

| Deep-   | PLLs                     | NPLDO off              | 1, LPMOD = 10,<br>WFI or WFE                | Any event(or interrupt | Run / Run1 | + NPLDO                  |

| sleep 2 | 3. LPLDO instead of      | LPLDO on               |                                             | when SEVONPEND         | / Run2     | wakeup                   |

|         | NPLDO                    |                        |                                             | is 1) from EXTI for    |            | time+Flash               |

|         | 4. COREOFF0 /            |                        |                                             | WFE                    |            | wakeup time              |

|         | SRAM1 / COREOFF1         |                        |                                             |                        |            |                          |

|         | power-off.               |                        |                                             |                        |            |                          |

|         | 1. The 1.1V domain is    |                        |                                             |                        |            | IRC16M                   |

|         | power off                | NPLDO off<br>LPLDO off | SLEEPDEEP =<br>1, LPMOD = 11,<br>WFI or WFE | 1. NRST pin            |            | wakeup time,             |

| Standby | 2. Disable IRC16M,       |                        |                                             | 2. WKUP pins           | Run        | + NPLDO                  |

| otanaby | IRC48M, HXTAL and        |                        |                                             | 3. FWDGT reset         | Run        | wakeup                   |

|         | PLLs                     |                        |                                             | 4. RTC                 |            | time+Flash               |

|         |                          |                        |                                             |                        |            | wakeup time              |

| BKP_ON  | All $V_{DD}$ / 1.1V core | NPLDO off              | V <sub>DD</sub> off                         | V <sub>DD</sub> on     | Run        | V <sub>DD</sub> power on |

| LY      | domain power off         | LPLDO off              |                                             |                        | i tuii     | sequence                 |

## 2.3. Methods to reduce power consumption

## System clock configuration

Clock prescaler can be configured with clock frequencies in the AHB and APBx domains. In Run mode, the system clock value is reduced by a clock pre-divider to provide the required clock for the peripherals and to avoid power loss due to overclocking. When peripherals are not in use, power consumption is further reduced through APBx and AHB gated clock disabling.

## Peripheral clock gating

The more peripherals are activated, the more power is consumed. By controlling the clock that does not use peripherals, energy saving is achieved.

## I/O configuration

All unused pins should be configured as analog inputs, in which case the Schmidt trigger is disabled and each I / O consumes zero, avoiding the creation of additional current. For output,

the lowest I / O speed is recommended. Do not activate the pull-up or pull-down configuration, if it is not necessary. Users also need to disable clock output pins when they are not needed.

## Using Direct Memory Access (DMA)

Peripherals can access data through DMA, which not only improves performance but also reduces power consumption. Before the DMA transfer ends, the CPU can enter sleep mode to achieve lower power consumption for the application.

### Use low power mode

Entering low power mode reduces average application power consumption. In the management of power mode switching, the requirements of application power consumption, wake up source, wake up time and peripheral operation are considered. In low power mode, if the GPIO has external component input / output, you are advised to set the input to pull-up / pull-down and output push-pull to ensure that the GPIO stays stationary when it is idle.

### Use low-power functional peripherals

Some of the GD32L233 peripherals feature low power consumption, such as LPTIMER and LPUART, which can achieve the required functions and performance while minimizing the power consumption. LPTIMER is a 32-bit timer that can operate in all power modes except Standby mode. Low power universal synchronous asynchronous receiver transmitter (LPUART) provides a low power flexible and convenient serial data exchange interface.

#### Set a low core voltage

The LDO (voltage regulator) powers the internal digital power. Setting a low core voltage is a simple and straightforward method to reduce power consumption. LDO that power the 1.1V domain and remain enabled after reset can be configured to work in different states: It includes Sleep mode (1.1V fully powered state, 0.9V fully powered state and low power state), Deep sleep mode / Deep sleep mode 1 / Deep sleep mode 2 (fully powered state or low power state) and standby mode (off state). In standby mode, the 1.1V domain is directly closed to greatly reduce power consumption, but the register content in the domain is lost, including internal RAM.

### Execute code from the SRAM

When the MCU is operating at normal or low power, code is executed from the SRAM and the flash memory can go into sleep / power down mode, further reducing power consumption.

#### Shut down SRAM1

SRAM1 (0x20004000~0x20007FFF) can be powered off independently. SRAM1 is powered on by default after the system is reset. In order to reduce the power consumption of Run mode / Run mode 1 / Run mode 2, SRAM1 can be powered off. To further reduce the power consumption of low power modes (Sleep mode / Sleep Mode 1 / Sleep mode 2 / Deep sleep mode / Deep sleep mode 1 / Deep sleep mode 2), SRAM1 can be powered off before entering low power mode.

## COREOFF1 Power domain is powered off

COREOFF1 domain can be powered off separately. COREOFF1 domain is powered off by default after the system is reset. The COREOFF1 domain needs to be powered on when the COREOFF1 domain module is used. To reduce the power consumption of Run mode / Run Mode 1 / Run Mode 2, power off the COREOFF1 domain. To further reduce the power consumption of low power modes (Sleep mode / Sleep Mode 1 / Sleep mode 2 / Deep sleep mode / Deep sleep mode 1 / Deep sleep mode 2), the COREOFF1 domain can be turned off before entering low power mode. COREOFF1 power domain contains the CAU module.

# 3. Summary

Embedded programs need to reduce power consumption when executing programs for complex real-time applications. For a given manufacturing process and wafer area, power consumption is largely determined by two dynamically controlled factors: voltage and frequency. In GD32L233 devices, LDO provides a fixed voltage for most logic circuits to minimize power consumption, while clock sources, cascaded clock prescaler, gating techniques, and peripheral clock management allow only necessary logic gates to activate. All these methods can reduce power consumption in operating mode. At the same time, the performance and power consumption of various power saving modes are considered to provide users with flexible choices.

# 4. Revision history

## Table 4-1. Revision history

| Revision No. | Description     | Date        |

|--------------|-----------------|-------------|

| 1.0          | Initial Release | Apr.7, 2023 |

### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2023 GigaDevice - All rights reserved