# GigaDevice Semiconductor Inc.

# Migration from GD32E230 series to GD32E235 series

Application Note AN169

# **Table of Contents**

| Tab  | ole of Contents                       |    |

|------|---------------------------------------|----|

| List | t of Figures                          | 3  |

|      | t of Tables                           |    |

|      | Introduction                          |    |

| 2.   | Introduction to hardware differences  | 6  |

| 3.   | Comparison of resource and peripheral | 7  |

| 4.   | Program Migration                     | 8  |

| 5.   | Revision history                      | 10 |

# **List of Figures**

| Figure 4- 1. Comparison of Write Protect Registers (FMC_WP) Differences between GD32E230x | (X |

|-------------------------------------------------------------------------------------------|----|

| and GD32E235xx devices                                                                    | 8  |

| Figure 4- 2. The difference of "gd32e23x_fmc. h" document                                 | 8  |

| Figure 4- 3. The GD32E233xx series comparator can be configured in high hysteresis mod    | e, |

| while the GD32E235xx series comparator cannot be configured in high hysteresis mode       | 9  |

# **List of Tables**

| Table 3-1. GD32E235xB device | ces features and peripheral list |

|------------------------------|----------------------------------|

| Table 5-1. Revision history  |                                  |

#### Introduction

The GD32E235xx device is a new 32-bit general-purpose microcontroller based on the Arm® Cortex®-M23 core. It has very high resource similarity with the GD32E230xx series, and this application note aims to help you quickly port applications from the GD32E230xx series microcontroller to the GD32E235xx series microcontroller.

In order to make better use of the information in this application note, you need to download it from the website www.GD32MCU.com, such as datasheet, user manual, official code and various development tools.

## 2. Introduction to hardware differences

The definition of pins for GD32E235xx series chips and GD32E230xx series devices in the same packaging is completely the same.

## 3. Comparison of resource and peripheral

The internal resources of GD32E235xx and GD32E230xx devices with the same suffix are consistent. In addition, GD32E235 has added a chip model with a FLASH capacity of 128KB and a RAM capacity of 16KB: GD32E235xB. As shown in <u>Table 3-1. GD32E235xB devices</u> features and peripheral list.

Table 3-1. GD32E235xB devices features and peripheral list

| Part Number  |              | GD32E235xx         |                    |                    |  |  |  |  |  |  |

|--------------|--------------|--------------------|--------------------|--------------------|--|--|--|--|--|--|

|              |              | KBU6               | КВТ6               | СВТ6               |  |  |  |  |  |  |

|              | FLASH(KB)    | 128 <sup>(1)</sup> | 128 <sup>(1)</sup> | 128 <sup>(1)</sup> |  |  |  |  |  |  |

|              | SRAM(KB)     | 16 <sup>(1)</sup>  | 16 <sup>(1)</sup>  | 16 <sup>(1)</sup>  |  |  |  |  |  |  |

|              | General      | 5                  | 5                  | 5                  |  |  |  |  |  |  |

|              | timer(16bit) | (2, 13-16)         | (2, 13-16)         | (2, 13-16)         |  |  |  |  |  |  |

|              | Advanced     | 1                  | 1                  | 1                  |  |  |  |  |  |  |

| ဟု           | timer(16bit) | (0)                | (0)                | (0)                |  |  |  |  |  |  |

| Timers       | SysTick      | 1                  | 1                  | 1                  |  |  |  |  |  |  |

| -            | Basic        | 1                  | 1                  | 1                  |  |  |  |  |  |  |

|              | timer(16bit) | (5)                | (5)                | (5)                |  |  |  |  |  |  |

|              | Watchdog     | 2                  | 2                  | 2                  |  |  |  |  |  |  |

|              | RTC          | 1                  | 1                  | 1                  |  |  |  |  |  |  |

|              | USART        | 2                  | 2                  | 2                  |  |  |  |  |  |  |

| <u>i</u> £   |              | (0-1)              | (0-1)              | (0-1)              |  |  |  |  |  |  |

| ctiv         | I2C          | 2                  | 2                  | 2                  |  |  |  |  |  |  |

| Connectivity |              | (0-1)              | (0-1)              | (0-1)              |  |  |  |  |  |  |

|              | SPI/I2S      | 2/1                | 2/1                | 2/1                |  |  |  |  |  |  |

|              |              | (0-1)/(0)          | (0-1)/(0)          | (0-1)/(0)          |  |  |  |  |  |  |

| GPIO         |              | 27                 | 25                 | 39                 |  |  |  |  |  |  |

| CMP          |              | 1                  | 1                  | 1                  |  |  |  |  |  |  |

|              | EXTI         | 16                 | 16                 | 16                 |  |  |  |  |  |  |

|              | Units        | 1                  | 1                  | 1                  |  |  |  |  |  |  |

|              | Channels     | 10                 | 10                 | 10                 |  |  |  |  |  |  |

| ADC          | (External)   |                    |                    |                    |  |  |  |  |  |  |

|              | Channels     | 2                  | 2                  | 2                  |  |  |  |  |  |  |

|              | (Internal)   |                    |                    |                    |  |  |  |  |  |  |

|              | Package      | QFN32              | LQFP32             | LQFP48             |  |  |  |  |  |  |

Note: (1) Compared with GD32E230x8 devices with the same packaging, these three new devices have the same resources except for the difference in FLASH capacity and SRAM capacity.

### 4. Program Migration

#### 4.1 Differences in FMC

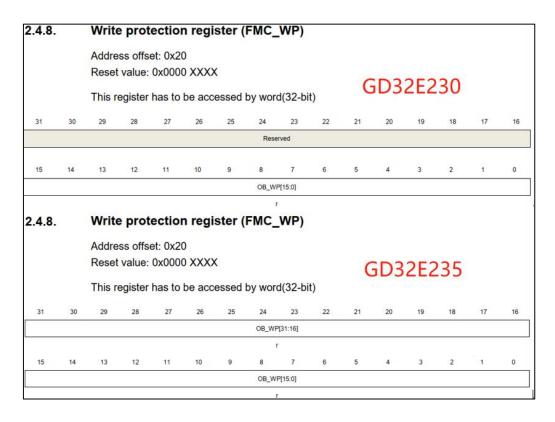

From the previous section, it can be seen that the FLASH capacity of GD32E235xB is larger, and there is a difference in the number of bits in the write protect register (FMC\_WP) between GD32E235xx and GD32E230xx devices. As shown in <a href="Figure 4-1">Figure 4-1</a>. Comparison of Write Protect Registers (FMC WP) Differences between GD32E230xx and GD32E235xx devices.

Figure 4- 1. Comparison of Write Protect Registers (FMC\_WP) Differences between GD32E230xx and GD32E235xx devices

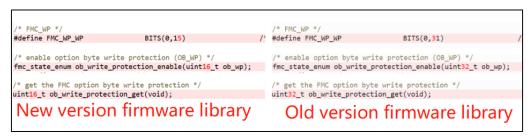

The new version firmware library GD32E23x\_Firmware\_Library(Version 2.0.0 and above) has made modifications to the "gd32e23x\_fmc.h" and "gd32e23x\_fmc.c" documents in order to be compatible with GD32E235xB. As shown in *Figure 4-2. The difference of "gd32e23x fmc. h" document*. The detailed functions can be found in the "gd32e23x\_fmc. c" document.

Figure 4- 2. The difference of "gd32e23x\_fmc. h" document

#### Migration from GD32E230 series to GD32E235 series

When porting from GD32E230xx to GD32E235xx or from GD32E235xx to GD32E230xx, it is necessary to pay attention to whether the flash size is compatible and modify the two documents "gd32e23x\_fmc. h" and "gd32e23x\_fmc. c". When replacing chips with flash capacities below 128KB, if the files "gd32e23x\_fmc. h" and "gd32e23x\_fmc. c" are not modified, it will not affect the functionality of the chip.

#### 4.2 Differences in Comparator

The hysteresis levels of the GD32E235xx series and GD32E230xx series comparators can be configured, but the GD32E235xx series cannot be configured as high hysteresis mode. If the GD32E235xx comparator operates in high hysteresis mode, it will result in functional errors with incorrect comparator results, When porting from GD32E230xx to GD32E235xx, this issue needs to be noted.

Figure 4- 3. The GD32E233xx series comparator can be configured in high hysteresis mode, while the GD32E235xx series comparator cannot be configured in high hysteresis mode

| 11.4.1.                            |          | Control/status register (CMP_CS)                        |                                                                    |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

|------------------------------------|----------|---------------------------------------------------------|--------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------|------------|---------|----------|---------|----------|----------|-----------|--------|-------|-------|

|                                    |          | Address offset: 0x00                                    |                                                                    |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

|                                    |          | Reset value: 0x0000 0000                                |                                                                    |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

| This register has to               |          |                                                         |                                                                    |            | b be accessed by word (32-bit)                                                          |            |         |          |         |          |          |           |        |       |       |

| 31                                 | 30       | 29                                                      | 28                                                                 | 27         | 26                                                                                      | 25         | 24      | 23       | 22      | 21       | 20       | 19        | 18     | 17    | 16    |

|                                    |          |                                                         |                                                                    |            |                                                                                         |            | Rese    | erved    |         |          |          |           |        |       |       |

| 15                                 | 14       | 13                                                      | 12                                                                 | 11         | 10                                                                                      | 9          | 8       | 7        | 6       | 5        | 4        | 3         | 2      | 1     | 0     |

| CMPLK                              | CMPO     | CMPH                                                    | ST[1:0]                                                            | CMPPL      | С                                                                                       | MPOSEL[2:  | 0]      | Reserved | CI      | MPMSEL[2 | :0]      | CMP       | M[1:0] | CMPSW | CMPEN |

| rwo                                | r        | rv                                                      | wr                                                                 | rw/r       |                                                                                         | rwr        |         |          |         | rw/r     |          | n         | w/r    | rw/r  | rwr   |

| Bits                               |          | Fields                                                  |                                                                    |            | Descri                                                                                  | ptions     |         |          |         |          |          |           |        |       |       |

| 31:16                              |          | Reserv                                                  | ed                                                                 |            | Must be kept at reset value                                                             |            |         |          |         |          |          |           |        |       |       |

| 15                                 | 15 CMPLK |                                                         |                                                                    |            | CMP lock                                                                                |            |         |          |         |          |          |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | This bit could set all control bits of CMP as read-only. This bit is write-once. It can |            |         |          |         |          |          |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | only be cleared by a system reset once It is set by software.                           |            |         |          |         |          |          |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | 0: CMP_CS[15:0] bits are read-write                                                     |            |         |          |         |          |          |           |        |       |       |

| 1: CMP_CS[15:0] bits are read-only |          |                                                         |                                                                    |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

| 14 CMPO                            |          |                                                         |                                                                    | CMP output |                                                                                         |            |         |          |         |          |          |           |        |       |       |

|                                    |          | This is a copy of CMP output state, which is read only. |                                                                    |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

|                                    |          |                                                         | 0: Non-inverting input below inverting input and the output is low |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | 1: Non-                                                                                 | -inverting | g input | above in | verting | input a  | nd the o | output is | high   |       |       |

| 13:12                              |          | CMPHS                                                   | ST[1:0]                                                            |            | CMP h                                                                                   | ysteresis  | S       |          |         |          |          |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | These                                                                                   | bits are   | used to | control  | the hys | teresis  | level.   |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | 00: No                                                                                  | hysteres   | sis     |          |         |          |          |           |        |       |       |

|                                    |          |                                                         |                                                                    |            | 01: Low hysteresis                                                                      |            |         |          |         |          |          |           |        |       |       |

|                                    |          |                                                         | 10: Medium hysteresis                                              |            |                                                                                         |            |         |          |         |          |          |           |        |       |       |

|                                    | [        |                                                         |                                                                    |            | 11: High hysteresis                                                                     |            |         |          |         |          |          |           |        |       |       |

## 5. Revision history

Table 5-1. Revision history

| Revision No. | Description     | Date       |

|--------------|-----------------|------------|

| 1.0          | Initial Release | Aug.8 2023 |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2023 GigaDevice – All rights reserved